#### **Features**

- Compliance with

- PCle Gen 3 (8Gb/s) X4 Lane with L1.2 support

- Compliant with PCIe Express 3.1

- NVMe 1.3 register interface and command set<sup>1</sup>

- Capacities

#### Bics4:

3D TLC NT/WT: 512GB,1TB,2TB

#### Bics3:

- 3D TLC NT/WT: 1TB

- Data Protection and Reliability

- Support DDR3/DDR3L External DRAM Buffer.

- Performance-optimized LDPC engine provides maximum error correction capability for 2D TLC as well as 3D TLC.

- SECDED2 SRAM ECC error handling and prevention on major memory buffers.

- RAID engine provides multi-page protection for NAND flash data.

- Supports 4 flash channels with 4 chip enable (CE) pins per channel.

- Supports ONFI 4.0/3.0 and Toggle 3.0/2.0 interface, frequency up to 667 MT/s.

- Programmable driving strength fits different types of NAND configurations.

- MTBF

- > 2,000,000 hours

- Temperature ranges

#### Operating:

Standard: 0°C to 70°CIndustrial: -40°C to 85°C

### Storage:

-55°C to 95°C

- Supply voltage

- 3.3 V ±5%

- Form factor

- PCle

- Shock & Vibration

- Shock: 1500G@0.5ms

- Vibration: 20 G

- Certification and Compliance

- FCC

- CE

- RoHs

- NAND Flash Type

- 3D TLC

# **TABLE OF CONTENTS**

| 1. | Proc  | duct Description                  | 5  |

|----|-------|-----------------------------------|----|

| 1  | .1.   | Product Overview                  | 5  |

| 1  | .2.   | Block Diagram                     | 6  |

| 2. | Proc  | duct Specification                | 7  |

| 2  | 2.1.  | Capacity                          | 7  |

| 2  | 2.2.  | Performance                       | 7  |

| 2  | 2.3.  | Software Function                 | 7  |

| 2  | 2.4.  | Power shield function             | 8  |

| 3. | Relia | ability Specifications            | 9  |

| 3  | 3.1.  | Environmental Conditions          | 9  |

| 3  | 3.2.  | TBW                               | 9  |

| 4. | Spe   | cification                        | 10 |

| 4  | l.1.  | Overlook                          | 10 |

| 4  | l.2.  | Dimension                         | 10 |

| 4  | l.3.  | Electronic Specifications         | 11 |

| 4  | l.4.  | Error Detection and Correction    | 12 |

| 4  | l.5.  | Wear-Leveling                     | 12 |

| 4  | l.6.  | Bad Blocks Management             | 12 |

| 4  | l.7.  | Mean Time Between Failures (MTBF) | 12 |

| 4  | l.8.  | Endurance                         | 13 |

| Δ  | 1.9   | Power Characteristics             | 13 |

# **Revision History**

| Rev | Date       | Description   |

|-----|------------|---------------|

| 1.0 | 2022/09/12 | First Release |

## 1. Product Description

### 1.1. Product Overview

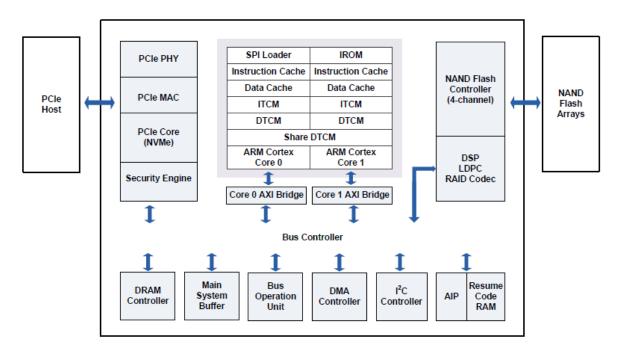

This SSD is a NVMe Express DRAM SSD designed as the standard M.2 form factor with PCIe interface and TLC NAND Flash. This SSD supports PCIe Gen III, and it is compliant with NVMe 1.3 providing excellent performance. Moreover, it adopts TLC NAND Flash providing high endurance and reliability. With sophisticated error detection and correction (ECC) functions.

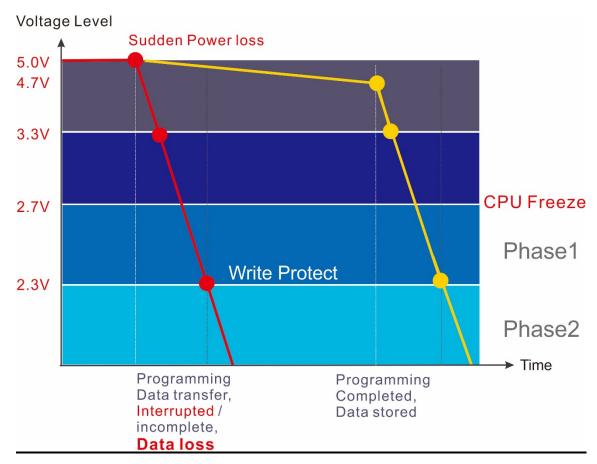

Another innovative design feature is worth mention is "Power Shield", excellent electronic circuit design provides high efficiency power protection capacitor charging efficiency, when a suddenly power failure can protect the integrity of the data write. This SSD is the perfect storage device for industrial PCs, Vehicle System, Professional-Grade Photography System.

This SSD is integrated with Silicom Motion controller which provides both low power consumption and efficient heat dissipation, working together, maximizes the reliability and endurance to respond the growing need for more data storage space.

# 1.2. Block Diagram

# 2. Product Specification

## 2.1. Capacity

| Raw Capacity | Capacity  | LBA           |

|--------------|-----------|---------------|

| 512GB        | 447.11 GB | 937,703,088   |

| 1 TB         | 894.24 GB | 1,875,385,008 |

| 2 TB         | 1788.5 GB | 3,750,748,848 |

### 2.2. Performance

■ 3D TLC (Bics4)

| Capacity              | 512GB      | 1TB         | 2TB         |

|-----------------------|------------|-------------|-------------|

| Sequential Read(Max)  | 3258MB/sec | 3460 MB/sec | 3462 MB/sec |

| Sequential Write(Max) | 939 MB/sec | 1883 MB/sec | 2899 MB/sec |

#### ■ 3D TLC (Bics3)

| Capacity              | 1TB         |

|-----------------------|-------------|

| Sequential Read(Max)  | 3440 MB/sec |

| Sequential Write(Max) | 1852 MB/sec |

#### Notes:

- 1. Performance may base on SSD capacity, hardware test platform, test software, operating system and other system variables.

- 2. The performance provided is the highest of the same capacity combinations.

The actual speed will be different because the ICs and channels are different from the quantity.

### 2.3. Software Function

- ECC Scheme

- UART function

- **■** GPIO

- S.M.A.R.T

- TRIM

## 2.4. Power shield function

Excellent Power Shield function, when a suddenly power failure can protect the integrity of the data write.

# 3. Reliability Specifications

## 3.1. Environmental Conditions

Environmental specifications are following MIL-STD-810F, as following table.

| Environment           | Specification                                      |

|-----------------------|----------------------------------------------------|

| Storage Temperature   | -55°C ~ +95°C                                      |

| Operating Temperature | 0°C to 70°C (Standard); -40°C to 85°C (Industrial) |

| Vibration             | 20G(7~2K Hz, 3 axes)                               |

| Shock                 | 1500G@0.5ms                                        |

| Humidity              | Relative Humidity: 10-95%, non-condensing          |

| MTBF                  | >2,000,000 hours                                   |

Note1: Vibration reference standard "IEC 60068-2-6"

Note2: Shock reference standard "IEC 60068-2-27"

Note3: MTBF condition," Telcordia SR-332"

## 3.2. TBW

| Capacity | TBW     |

|----------|---------|

| 512GB    | 769 TB  |

| 1TB      | 1538 TB |

| 2ТВ      | 3077 TB |

# 4. Specification

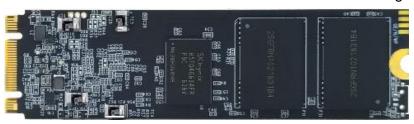

## 4.1. Overlook

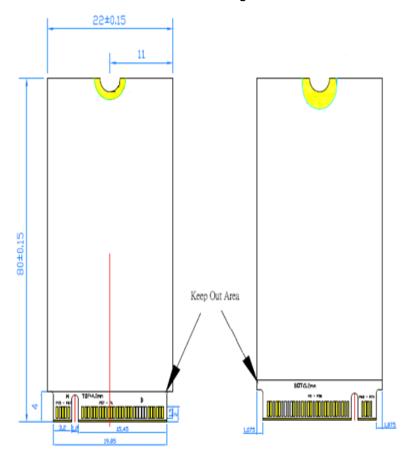

The overlook views of M.2 2280 Module are illustrated in Figure 1.

Figure 1: M.2 2280 Module Overlook Diagram

## 4.2. Dimension

The Dimensions of M.2 2280 Module are illustrated in Figure 1.

Figure 1: M.2 2280 Module Dimensions

# 4.3. Electronic Specifications

## 4.4.1 PCIe interface Signals

| Signal  | Ball NO. | Туре   | Description                                 | PU/PD |

|---------|----------|--------|---------------------------------------------|-------|

| PORXP   | F1       | Input  |                                             | 1     |

| PORXN   | G1       | Input  |                                             | -     |

| P1RXP   | J1       | Input  |                                             | -     |

| P1RXN   | K1       | Input  | DCIa Daggivad data differential pair        | -     |

| P2RXP   | M1       | Input  | PCIe Received data differential pair        | -     |

| P2RXN   | N1       | Input  |                                             | -     |

| P3RXP   | R1       | Input  |                                             | -     |

| P3RXN   | T1       | Input  |                                             | -     |

| POTXP   | G2       | Output |                                             | -     |

| P0TXN   | H2       | Output |                                             | -     |

| P1TXP   | K2       | Output |                                             | -     |

| P1TXN   | L2       | Output | DCIo Transport data differential main       | -     |

| P2TXP   | N2       | Output | PCIe Transmit data differential pair        | -     |

| P2TXN   | P2       | Output |                                             | -     |

| P3TXP   | T2       | Output |                                             | -     |

| P3TXN   | U2       | Output |                                             | -     |

| REFCLKP | D2       | Input  | 100MHz positive input of differential input | -     |

|         |          |        | clock                                       |       |

| REFCLKN | D1       | Input  | 100MHz negative input of differential       | -     |

|         |          |        | input clock                                 |       |

| RREF    | J3       | Input  | Reference resistor connection for PCIe PHY  | -     |

### 4.4. Error Detection and Correction

The LDPC ECC engine executes parity generation and error detection/correction features, and enhances decoding throughput and data reliability. With LDPC of correction capability 1e-2 RBER, the hard and soft decoding mechanism provides powerful error correction. Hence the SSD can enhance the endurance and retention of TLC NAND and extends the SSD lifespan.

## 4.5. Wear-Leveling

Flash memory can be erased within a limited number of times. This number is called the erase cycle limit or write endurance limit and is defined by the flash array vendor. The erase cycle limit applies to each individual erase block in the flash device.

## 4.6. Bad Blocks Management

Bad Blocks are blocks that contain one or more invalid bits whose reliability are not guaranteed. The Bad Blocks may be presented while the SSD is shipped, or may generate during the life time of the SSD. When the Bad Blocks is detected, it will be flagged, and not be used anymore. The SSD implement Bad Blocks management and replacement, Error Correct Code to avoid data error occurred. The functions will be enabled automatically to transfer data from Bad Blocks to spare blocks, and correct error bit. After the reserved block less than 10 of each channel, the SSD will be locked, and cannot be read and written anymore. Host can send a vendor ATA command to unlock the SSD for backup data or system from SSD.

## 4.7. Mean Time Between Failures (MTBF)

**Failure Rate**: The total number of failures within an item population, divided by the total number of life units expended by that population, during a particular measurement interval under stated condition.

**Mean Time Between Failures (MTBF)**: A basic measure of reliability for repairable items: The mean number of life units during which all parts of the item perform within their specified limits, during a particular measurement interval under stated conditions.

| Product       | Condition                 | MTBF (Hours) |

|---------------|---------------------------|--------------|

| M.2 2280 PCle | Telcordia SR-332 GB, 25°C | >2,000,000   |

Table6: M.2 2280 PCIe MTBF

### 4.8. Endurance

Data Retention: 10 years.

Flash Endurance:

• TLC: 3,000 P/E Cycle

Wear-Leveling Algorithm: Support.Bad Blocks Management: Support.

Error Correct Code: Support..

### 4.9. Power Characteristics

### 4.9.1. Supply Voltage

| Parameter Specifications | Parameter Specifications |

|--------------------------|--------------------------|

| Input Voltage            | 3.3V +/- 5%              |

### 4.9.2. Power Consumption

| Parameter Specifications | Specifications (W) |

|--------------------------|--------------------|

| Idle (max.)              | 0.69W              |

| Active (max.)            | 6.6W               |

#### Notes:

- 1. The measured power voltage is 3.3V.

- 2. Its average value of power consumption is achieved based on 100% conversion efficiency.

Power Consumption may differ according to flash configuration and platform.