December 2011, First Edition (Japanese version) Febrary 2012, First Edition (English version)

(Note) Silk screen print in the above picture is a composite. The actual print may differ.

#### $\bullet$ Introduction $\bullet$

First of all, thank you for having purchased our LCD controller IC (KS-LTWV-SD (LVDS)) and the touch panel controller IC (KS-R8TPC or KS-R10TPC) (the "Product"). This hardware manual (the "Manual") provides an overview of the Product. We hope that you will read the Manual carefully and make use of it for efficient development.

#### Important Information

- 1. The Product and this Manual may change without notice. Before using the Product, obtain the newest catalog, manual, etc., from the company website.

- 2. The Product is not designed to be used in systems or devices that can cause death, injury, or serious physical or environmental damage directly due to any malfunction of the Product (life support device, nuclear facility equipment, aircraft, traffic control equipment, various safety devices, etc.). Danger and damage due to the Product being used in the foregoing systems or devices are the sole responsibility of the customer.

- 3. We assume no responsibility for any damages due to the use or the operation of the Product in a misguided or wrongful way.

- 4. The usage examples outlined herein are only an explanation of the Product functions. We assume no responsibility for any complaints, accidents, or any disadvantages which may be caused by the use on the basis of the examples outlined in this Manual.

# Table of Contents

| 1.  | Composition of the LCD Controller IC   |     |

|-----|----------------------------------------|-----|

|     | and the Touch Panel Controller         | P4  |

| 2.  | Overview and Features of the Product   | P4  |

| 3.  | System Configuration Diagram           | P6  |

| 4.  | Pins (Reference circuits)              | P7  |

| 5.  | Electrical Characteristics (DC, AC),   |     |

|     | Access Timing Specifications           | P19 |

| 6.  | Address Map                            | P24 |

| 7.  | Pixel Composition of the Screen        | P27 |

| 8.  | Displayed Data                         | P29 |

| 9.  | Drawing Function                       | P32 |

| 10. | Image Data Transfer Function           | P35 |

| 11. | Self-refresh Function                  | P42 |

| 12. | About the Registers                    | P43 |

| 13. | External Dimensions                    | P64 |

| 14. | Design Precautions                     | P65 |

| 15. | Handling Precautions                   | P66 |

| 16. | <b>Operating Condition Precautions</b> | P70 |

| 17. | Installation Method                    | P72 |

# 1. Composition of the LCD Controller IC and the Touch Panel Controller LCD

- KS-LTWV-SD (LVDS) (LCD controller IC)

KS-LTWV-SD (LVDS) is broadly applicable to the LVDS LCD, including WVGA

TFT LCD "GVTW70SPAH series" (manufacturer: SGD), etc.

- 2) KS-R8TPC or KS-R10TPC (Touch panel controller) KS-R8TPC is a CPU device with 2 channels, 8-bit A/D conversion (manufacturer: Renesas, model: R5F211B4SP).

KS-R10TPC is a CPU device with 2 channels, 10-bit A/D conversion (manufacturer: Renesas, model: R5F211B4SP).

(Manufacturer of the CPU and product number may change without notice.)

LCD display and touch panel control become possible by using the above set of two. Additionally, display is also possible using only the LCD controller IC.

### 2. Overview and Features of the Product

KS-LTWV-SD (LVDS) is an LCD controller developed for embedded systems, with the following characteristics.

- 1) This LCD controller is WVGA TFT color LCD-compatible (Interface is LVDS). The LCD controller is equipped with a built-in LVDS interface. We guarantee that signal distance for the LVDS is 2m.

- 2) The frame buffer memory is SDR SDRAM-compatible. When using the SDR SDRAM (2M×16-bits×4 banks), you can select a wide area of 2,048×1,024 pixels × 4 pages to 800×480 pixels.

- 3) Color can be displayed in 2 modes: 64 colors in 4,096 color mode (palette format)

× 2 pages and 65,536 color mode × 1 page.

- 4) By making the screen one page per area, 65,536 colors can be displayed. (There are function restrictions such as blinking, etc.).

- 5) Two-layer superimposed display is possible. (Only the 64 colors in 4,096 color mode).

- 6) When a flash-ROM is installed to the CPU bus, short videos can be played.

- 7) The Tiny-accelerator function allows high-speed drawing of lines and fill-ins of

Kenic system

rectangular shapes.

- 8) There is an automatic switch display function per pixel, which decreases the load on the CPU.

- 9) Design is easy with only knowledge of the Host-CPU. LCD expertise is not necessary

- 10) The Host-CPU is most compatible with the H8 Host-CPU (Hitachi) and SH Host-CPU. (Interface with 3.3V Host-CPU is possible.)

- 11) Connection with a touch panel controller in which the touch panel data is 10-bit (KS-R10TPC) is possible.

- 12) When writing the image data from the flash memory to the frame buffer memory (SDRAM), it is possible to not write the color specified by the register.

- 13) The SDRAM can be switched to a self-refresh state.

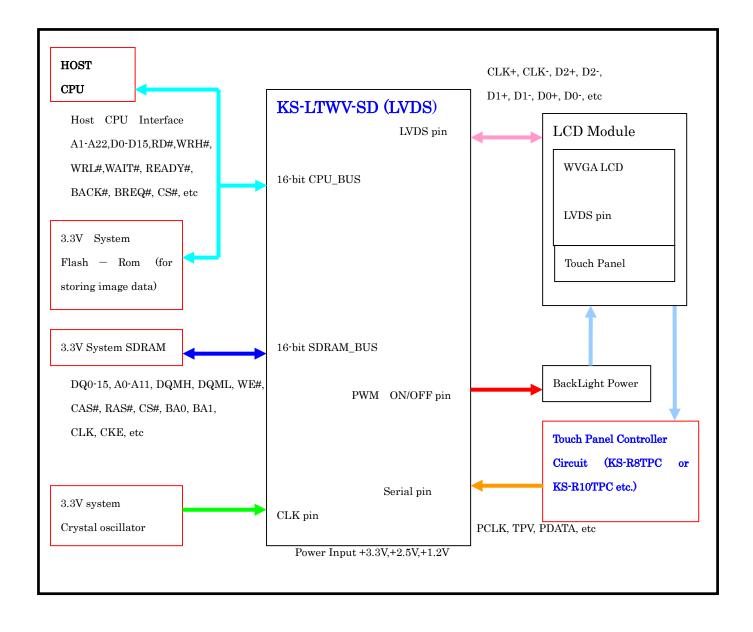

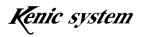

### 3. System Configuration Diagram

The outline framework for KS-LTWV-SD (LVDS) is as follows. The customer only needs to prepare a SDR SDRAM in order to complete the LCD controller. And, by preparing a large flash memory, the LCD controller reads data automatically, image display is also possible.

- Note 1. The blue areas indicate the LCD controller and the touch panel controller.

- Note 2. When the touch panel (KS-R8TPC or KS-R10TPC) is not necessary, its circuit part is deletable.

### 4. Pins

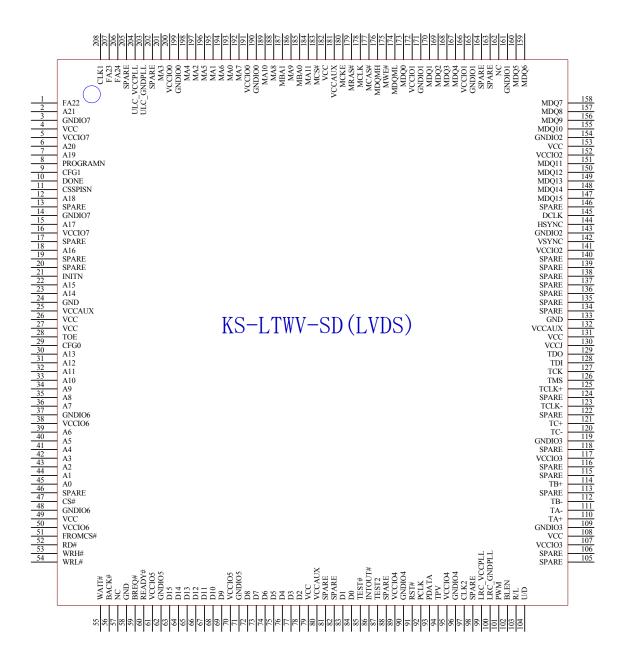

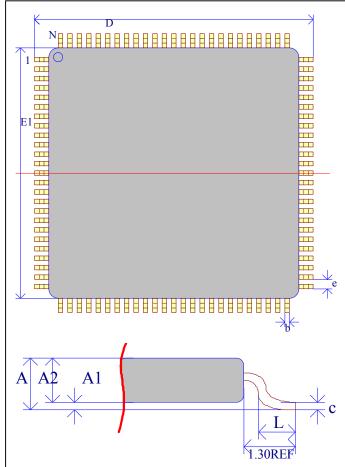

Diagram) Pinout Diagram

The following table indicates pin assignments (list of pin numbers and signal names) for KS-LTWV-SD (LVDS).

In this Manual, we have provided the reference circuits as examples. (However, operation of these circuits is not guaranteed. Be aware that the circuit may not operate due to certain circumstances and conditions.)

| Pin No | Pin Name | Interface                             | Pin No | Pin Name | Interface                                     |

|--------|----------|---------------------------------------|--------|----------|-----------------------------------------------|

| 1      | FA22     | Address signal for<br>FROM (output)   | 105    | SPARE    | No connection                                 |

| 2      | A21(*1)  | Generic Host-CPU<br>address bus (I/O) | 106    | SPARE    | No connection                                 |

| 3      | GNDIO7   | 0V                                    | 107    | VCCIO3   | +2.5 V                                        |

| 4      | VCC      | +1.2V                                 | 108    | VCC      | +1.2V                                         |

| 5      | VCCIO7   | +3.3V                                 | 109    | GNDIO3   | OV                                            |

| 6      | A20(*1)  | Generic Host-CPU                      | 110    | TA+      | To LCD panel                                  |

| 7      | A19(*1)  | address bus (I/O)                     | 111    | TA-      |                                               |

| 8      | PROGRAMN | 10k Pull-up                           | 112    | TB-      |                                               |

| 9      | CFG1     | 10k Pull-up                           | 113    | SPARE    | No connection                                 |

| 10     | DONE     | 10k Pull-up                           | 114    | TB+      | To LCD panel                                  |

| 11     | CSSPISN  | 4.7k Pull-up                          | 115    | SPARE    | No connection                                 |

| 12     | A18(*1)  | Generic Host-CPU<br>address bus (I/O) | 116    | SPARE    |                                               |

| 13     | SPARE    | No connection                         | 117    | VCCIO3   | +2.5V                                         |

| 14     | GNDIO7   | 0V                                    | 118    | SPARE    | No connection                                 |

| 15     | A17(*1)  | Generic Host-CPU<br>address bus (I/O) | 119    | GNDIO3   | 0V                                            |

| 16     | VCCIO7   | +3.3V                                 | 120    | TC-      | To LCD panel                                  |

| 17     | SPARE    | No connection                         | 121    | TC+      |                                               |

| 18     | A16(*1)  | Generic Host-CPU<br>address bus (I/O) | 122    | SPARE    | No connection                                 |

| 19     | SPARE    | No connection                         | 123    | TCLK-    | To LCD panel                                  |

| 20     | SPARE    |                                       | 124    | SPARE    | No connection                                 |

| 21     | INITN    | 10k Pull-up                           | 125    | TCLK+    | To LCD panel                                  |

| 22     | A15(*1)  | Generic Host-CPU<br>address bus (I/O) | 126    | TMS      | Signal for<br>configuration<br>10k Pull-up    |

| 23     | A14(*1)  |                                       | 127    | TCK      | Signal for<br>configuration<br>2.2k Pull-down |

| 24     | GND      | 0V                                    | 128    | TDI      | Signal for                                    |

| 25     | VCCAUX   | +3.3V                                 | 129    | TDO      | configuration                                 |

| 26     | VCC      | +1.2V                                 | 130    | VCCJ     | +3.3V                                         |

| 27     | VCC      |                                       | 131    | VCC      | +1.2V                                         |

| 28     | TOE      | 10k Pull-up                           | 132    | VCCAUX   | +3.3V                                         |

| 29     | CFG0     | 2.2k Pull-down                        | 133    | GND      | 0V                                            |

| 30     | A13(*1)  | Generic Host-CPU                      | 134    | SPARE    | No connection                                 |

| 31     | A12(*1)  | address bus (I/O)                     | 135    | SPARE    |                                               |

| 32     | A11(*1)  | _                                     | 136    | SPARE    |                                               |

| 33     | A10(*1)  | _                                     | 137    | SPARE    |                                               |

| 34     | A9(*1)   |                                       | 138    | SPARE    |                                               |

| 35     | A8(*1)   | _                                     | 139    | SPARE    |                                               |

| 36     | A7(*1)   |                                       | 140    | SPARE    |                                               |

Table 1) KS-LTWV-SD (LVDS)

-8-

| 37              | GNDIO6           | 0V                                    | 141               | VCCIO2           | +3.3V                       |

|-----------------|------------------|---------------------------------------|-------------------|------------------|-----------------------------|

| 38              | VCCIO6           | +3.3V                                 | 142               | VSYNC            | Frame signal                |

|                 |                  |                                       |                   |                  | output                      |

| 39              | A6(*1)           | Generic Host-CPU<br>address bus (I/O) | 143               | GNDIO2           | 0V                          |

| 40<br>41        | A5(*1)<br>A4(*1) | address bus (I/O)                     | 144<br>145        | HSYNC<br>DCLK    | No use                      |

| 41 42           | A3(*1)           | _                                     | $143 \\ 146$      | SPARE            | No connection               |

|                 |                  | _                                     |                   |                  |                             |

| 43              | A2(*1)           | _                                     | 147               | MDQ15            | SDR SDRAM data              |

| 44              | A1(*1)           | _                                     | 148               | MDQ14            | bus                         |

| 45<br>46        | A0(*1)<br>SPARE  |                                       | 149<br>150        | MDQ13            |                             |

| 46              | CS#              | No connection<br>Geniric Host-CPU     | 150               | MDQ12<br>MDQ11   |                             |

| 47              | 0.5#             | (Input)                               | 191               | MDQ11            |                             |

| 48              | GNDIO6           | 0V                                    | 152               | VCCIO2           | +3.3V                       |

| 49              | VCC              | +1.2V                                 | 153               | VCC              | +1.2V                       |

| 50              | VCCIO6           | +3.3V                                 | 154               | GNDIO2           | 0V                          |

| 51              | FROMCS#(*1)      | Chip select signal for                | 155               | MDQ10            | SDR SDRAM data              |

|                 |                  | FROM (Tristate<br>output)             |                   |                  | bus                         |

| 52              | RD#(*1)          | Generic Host-CPU                      | 156               | MDQ9             |                             |

| 50              | WDII#            | (I/O)                                 | 150               | MDOO             |                             |

| 53              | WRH#<br>WRL#     | Geniric Host-CPU<br>(input)           | 157               | MDQ8             |                             |

| $\frac{54}{55}$ | WAIT#            | Generic Host-CPU                      | $158 \\ 159$      | MDQ7<br>MDQ6     |                             |

| 55              | VV/A11#          | (Tristate output)                     | 109               | MDQ0             |                             |

| 56              | BACK#            | Geniric Host-CPU<br>(input)           | 160               | MDQ5             |                             |

| 57              | NC               | No connection                         | 161               | GNDIO1           | 0V                          |

| 58              | GND              | 0V                                    | 162               | NC               | No connection               |

| 59              | BREQ#            | Geniric Host-CPU                      | 163               | SPARE            |                             |

| 60              | READY#           | (output)                              | 164               | SPARE            |                             |

| 61              | VCCIO5           | +3.3V                                 | 165               | GNDIO1           | 0V                          |

| 62              | GNDIO5           | 0V                                    | 166               | VCCIO1           | +3.3V                       |

| 63              | D15              | Generic Host-CPU                      | 167               | MDQ4             | SDR SDRAM data              |

| 64              | D14              | data bus (I/O)                        | 168               | MDQ3             | bus                         |

| 65              | D13              | _                                     | 169               | MDQ2             |                             |

| 66              | D12              | _                                     | 170               | MDQ1             | 0V                          |

| 67<br>68        | D11<br>D10       | _                                     | $\frac{171}{172}$ | GNDIO1<br>VCCIO1 | +3.3V                       |

| <u>68</u>       | D10<br>D9        | _                                     | 172<br>173        | MDQ0             | SDR SDRAM data              |

| 05              | 100              |                                       | 115               | MDQU             | bus                         |

| 70              | VCCIO5           | +3.3V                                 | 174               | MDQML            | SDR SDRAM                   |

| 71              | GNDIO5           | 0V                                    | 175               | MWE#             | control signal              |

| 72              | D8               | Generic Host-CPU                      | 176               | MDQMH            |                             |

| 73              | D7               | data bus (I/O)                        | 177               | MCAS#            |                             |

| 74              | D6               |                                       | 178               | MCLK             | SDR SDRAM<br>clock          |

| 75              | D5               | 7                                     | 179               | MRAS#            | SDR SDRAM                   |

| 76              | D4               |                                       | 180               | MCKE             | control signal              |

| 77              | D3               |                                       | 181               | VCCAUX           | +3.3V                       |

| 78              | D2               |                                       | 182               | VCC              | +1.2V                       |

| 79              | VCC              | +1.2V                                 | 183               | MCS#             | SDR SDRAM<br>control signal |

| 80              | VCCAUX           | +3.3V                                 | 184               | MA11             | SDR SDRAM<br>address bus    |

| 81              | SPARE            | No connection                         | 185               | MBA0             | SDR SDRAM                   |

| 82              | SPARE            | -                                     | 186               | MA9              | bank address SDR SDRAM      |

|                 |                  |                                       |                   |                  | address bus                 |

-9-

| 83  | D1         | Generic Host-CPU                   | 187 | MBA1       | SDR SDRAM                |

|-----|------------|------------------------------------|-----|------------|--------------------------|

|     |            | data bus (I/O)                     |     |            | bank address             |

| 84  | D0         | 7                                  | 188 | MA8        | SDR SDRAM                |

| 85  | TEST#      | +3.3V                              | 189 | MA10       | address bus              |

| 86  | INTOUT#    | Interrupt request<br>output        | 190 | GNDIO0     | 0V                       |

| 87  | TEST2      | No connection (test signal output) | 191 | VCCIO0     | +3.3V                    |

| 88  | SPARE      | No connection                      | 192 | MA7        | SDR SDRAM                |

| 89  | VCCIO4     | +3.3V                              | 193 | MA0        | address bus              |

| 90  | GNDIO4     | 0V                                 | 194 | MA6        |                          |

| 91  | RST#       | Reset circuit                      | 195 | MA1        |                          |

| 92  | PCLK       | To KS-R8TPC                        | 196 | MA5        |                          |

| 93  | PDATA      |                                    | 197 | MA2        |                          |

| 94  | TPV        |                                    | 198 | MA4        |                          |

| 95  | VCCIO4     | +3.3V                              | 199 | GNDIO0     | 0V                       |

| 96  | GNDIO4     | 0V                                 | 200 | VCCI00     | +3.3V                    |

| 97  | CLK2       | Reset circuit                      | 201 | MA3        | SDR SDRAM<br>address bus |

| 98  | SPARE      | No connection                      | 202 | SPARE      | No connection            |

| 99  | LRC_VCCPLL | +3.3PLL                            | 203 | ULC_GNDPLL | 0V                       |

| 100 | LRC_GNDPLL | 0V                                 | 204 | ULC_VCCPLL | +3.3 PLL                 |

| 101 | PWM        | To backlight part                  | 205 | SPARE      | No connection            |

| 102 | BLEN       |                                    | 206 | FA24       | Address signal for       |

| 103 | R/L        | To LCD panel                       | 207 | FA23       | FROM (output)            |

| 104 | U/D        | 7 -                                | 208 | CLK1       | Clock etc.               |

Precautions

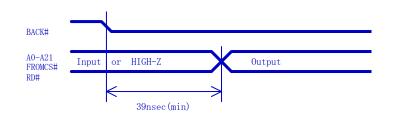

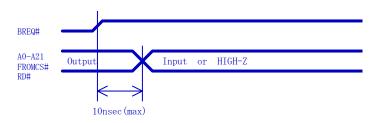

(\*1) These ports are in the following states during image data transfer and when image data transfer is not occurring (normal state).

• During image data transfer

| A21~A0  | •••   | Output |

|---------|-------|--------|

| FROMCS# | • • • | Output |

| RD#     | • • • | Output |

• Image data transfer not occurring (Normal state)

A21~A0· · · InputFROMCS#· · · Hi impedanceRD#· · · Input

# [Reference Circuits]

(1) Reference Circuit Diagram of the LCD Controller IC Area

(Connection and Precautions)

• Quartz Module

Although the quartz module contains the SG8002 (EPSON); any product with a frequency of 38.362MHz can be used.

There are two clock pins (No.97 pin and No.208 pin) for the LCD controller. Provide each clock from same quartz module.

• About the CPU Bus

Connect to Hitachi-manufactured H8 Host-CPU, SH-2 Host-CPU, or SH-3, 4 processor, etc.

For the address bus, connect the A22~A1 from the CPU to the A21~A0 pins of the LCD controller.

When using the H8 Host-CPU, SH-2 Host-CPU, or SH-3 processor, connect the WAIT# signal from the LCD controller to the WAIT# pin input of the CPU. Always pull up with a resistance of 4.7k~10k for the WAIT# signal. When using the SH-4 processor, connect the READY# signal from the LCD controller to the RDY# pin input of the CPU.

When installing the FROM for images and using the image data transfer function of the LCD controller, the LCD controller accesses the FROM for images, so it is necessary to release the CPU bus. In that case, connect the BREQ# signal and BACK# signal of the LCD controller to the BREQ# pin and BACK# pin of the CPU.

When transferring image data, I/O direction is switched for some signals of the CPU bus. Regarding the switch timing of the I/O direction, refer to "5. Electrical Characteristics (DC, AC), Access Timing Specifications".

Reset Signal

The LCD controller provides RESET# input pins for the LCD controller. The internal circuit is reset by ACTIVE LOW. Connect the reset signal used by the CPU, etc. Additionally, if there is noise on the reset signal line, mount a capacitor with the capacity of about 104 near the RESET# input pin, in order to prevent inadvertent resets.

- Connection to the SDR SDRAM Refer to "(2) Reference Circuit of the SDR SDRAM" below.

- Connection to the FROM for image Refer to "(3) Reference Circuit of the FROM for images" below.

- Connection to the LCD

Refer to "(4) Reference Circuit of the LCD I/F" below.

- Connection to the LED Backlight Circuit

Refer to "(5) Reference Circuit for Backlight I/F" below.

- Connection to the Touch Panel Controller (KS-R8TPC or KS-R10TPC) KS-R8TPC or KS-R10TPC can be connected directly. For more details, refer to "Touch panel controller IC KS-R8TPC hardware manual" or "Touch panel controller IC KS-R10TPC hardware manual".

When using the LCD controller only, use the control signals (PCLK, PDATA, TPV)

with the open state.

- Arrangement of the Bypass CapacitorBe particularly careful about the arrangement of the bypass capacitor. When a four-layer board is impossible, bring as close to the LSI VCC pin as possible.

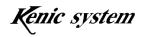

- Power Supply for PLL

PLL is used inside the LCD controller. As the LRC\_VCCPLL and ULC\_VCCPLL power supply pins for the PLL are susceptible to noise, make a single point connection (connect via a  $0\Omega$  resistor) with other power supplies as shown in the diagram below.

Moreover, in order to further eliminate the effect of noise, it is recommended to insulate from other power supplies using an inductor. (Replace  $0\Omega$  resistor with inductor.)

Inductor Specifications (Examples)

- **\square** Package size 0805 package (2×1.25)

- Rated current 1A

- Inductance 1µH and over

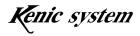

(2) Reference Circuit of the SDR SDRAM (IS42S16800E-7TL)

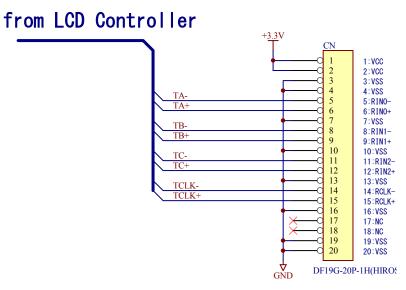

to LCD Controller

Be careful with the connection of the bypass capacitor; place near the VCC. Additionally, for the pattern length, make sure the distance from the LCD controller is under 10cm. It is recommended that the wiring use the fewest number of vias as possible, and that isometric wiring is used.

Use the SDR SDRAM with 7nS and under (IS42S16800E-7TL (ISSI), IS42S16800E-6TLI, etc.).

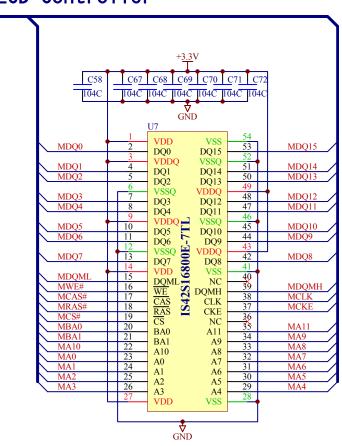

(3) Reference Circuit of FROM for images (S29GL512P10TFI)

The above diagram is the connection example to the flash memory "S29GL512P10TFI" (SPANSION).

# (4) Reference Circuit of the LCD I/F

• Connection example to WVGA-TFT LCD (SGD)

The above diagram is the reference circuit diagram when connecting the WVGA-TFT LCD "GVTW70SPAH series" (7 inch).

Kenic system

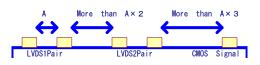

About the LVDS Pattern

For the LVDS pattern wiring, be careful of the following points as much as possible.

- The wiring should use the fewest number of vias between the LCD controller and connector.

- When setting a via on one side of a differential pairing, also set a via on the other signal line, making the same state.

- $\boldsymbol{\cdot}$  Use isometric wiring between the LCD controller and connector.

- The distance between the LCD controller and connector should be as short as possible.

- Do not place a divided slit in the internal layer GND pattern of the LVDS signal.

- The wiring interval A between differential pairs should be at a minimum.

- $\cdot$  The wiring interval between each pair should be A×2 or more.

- $\boldsymbol{\cdot}$  The LVDS and CMOS or TTL wiring interval should be A×3 or more.

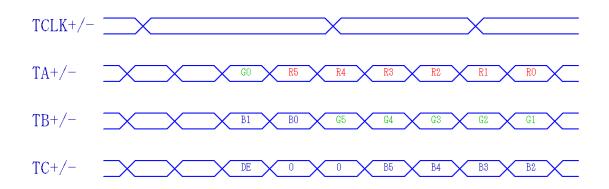

• Signal mapping of the LVDS

The following diagram is a signal map of the LVDS signal output data.

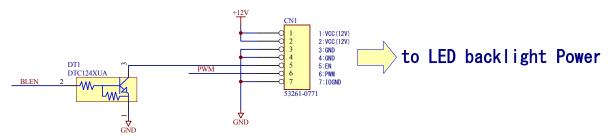

# (5) Reference Circuit for Backlight I/F (reference)

• Reference circuit for LED backlight(Kenic System: KSLBC-4(D3))

The above diagram is an example connection between the LED backlight power supply "KSLBC-4 (D3)" (Kenic system) (sold separately) and the LCD controller. This LED backlight power supply can be used for the following LCDs: WVGA-TFT LCD "GVTW70SPAH series" (7 inch) (manufacturer: SGD).

When the EN signal is open, the backlight is in the ON state. By connecting the BLEN signal outputted from the LCD controller to the open collector or digital transducer, ON/OFF for the backlight can be controlled.

Brightness of the backlight can be controlled by the PWM signal. The PWM frequency and ON width can be set by the register. For the setting method, refer to "11. About the registers". And, for the PWM input specification for the LED backlight power supply, refer to the LED backlight power supply specifications.

There are also LED backlight power supplys which are compatible with other LCDs. For more details, please make an inquiry to our sales staff.

# 5. Electrical Characteristics (DC, AC), Access Timing Specifications

| <ul> <li>Maxir</li> </ul> | num Ra | atings           |       |

|---------------------------|--------|------------------|-------|

| Item                      | Sign   | Rating           | Units |

| Power supply              | Vcc    | -0.5~1.32        | V     |

| voltage                   |        |                  |       |

| Power supply              | VCC    | $-0.5 \sim 3.75$ | V     |

| voltage                   | AUX    |                  |       |

| Power supply              | VCC    | $-0.5 \sim 3.75$ | V     |

| voltage                   | J      |                  |       |

| Power supply              | VCC    | -0.5~3.75        | V     |

| voltage                   | PLL    |                  |       |

| Output power              | VCC    | -0.5~3.75        | V     |

| supply voltage            | IO     |                  |       |

| Voltage added             |        | $-0.5 \sim 3.75$ | V     |

| to input or               |        |                  |       |

| tri-state I/O             |        |                  |       |

| Storage                   | TSTG   | -65~+150         | °C    |

| temperature               |        |                  |       |

| (Ambiance)                |        |                  |       |

| Junction                  | $T_j$  | +125             | °C    |

| temperature               |        |                  |       |

#### Recommended Operating Conditions

| _              | -        |       |       |       |

|----------------|----------|-------|-------|-------|

| Item           | Sign     | Min.  | Max.  | Units |

| Internal core  | Vcc      | 1.14  | 1.26  | V     |

| power supply   |          |       |       |       |

| voltage        |          |       |       |       |

| Auxiliary      | VCCAUX   | 3.135 | 3.465 | V     |

| power supply   |          |       |       |       |

| voltage        |          |       |       |       |

| PLL            | VCCPLL   | 3.135 | 3.465 | V     |

| power supply   |          |       |       |       |

| voltage        |          |       |       |       |

| I/O driver     | VCCIO0~2 | 3.135 | 3.465 | V     |

| power supply   | and 4~7  |       |       |       |

| voltage        | VCCIO3   | 2.375 | 2.625 | V     |

| IEEE1149.1     | VCCJ     | 3.135 | 3.465 | V     |

| test access    |          |       |       |       |

| port power     |          |       |       |       |

| supply voltage |          |       |       |       |

| Junction       | Tj       | 0     | 85    | °C    |

| temperature    |          |       |       |       |

| Ambient        | Та       | 0     | 60    | °C    |

| Operating      |          |       |       |       |

| temperature    |          |       |       |       |

The LCD controller requires +1.2V (core power supply voltage), +2.5V (VCCIO3 for LVDS), and +3.3V (VCCIO except for VCCAUX, VCCPLL, VCCJ and VCCIO3).

Kenic system

-19-

|         | ard (at recomm | ended ope       |       |      |       |

|---------|----------------|-----------------|-------|------|-------|

| Iter    | n              | Sign            | Min.  | Max. | Units |

| Input   | Hi             | V <sub>IH</sub> | 2.0   | 3.6  | V     |

| voltage |                |                 |       |      |       |

| Input   | Low            | VIL             | -0.3  | 0.8  | V     |

| voltage |                |                 |       |      |       |

| Output  | Hi             | Voh             | VCCIO |      | V     |

| voltage |                |                 | -0.4  |      |       |

| Output  | Low            | Vol             |       | 0.4  | V     |

| voltage |                |                 |       |      |       |

Single end IO DC Standard (at recommended operating conditions)

### LVDS Differential IO DC Standard (at recommended operating conditions)

| Item           | Sign                   | Test conditions          | Min.       | Rating     | Max.  | Units |

|----------------|------------------------|--------------------------|------------|------------|-------|-------|

| Output         | Vod                    | $(V_{OP}-V_{OM})$        | 250        | 350        | 450   | mV    |

| differential   |                        | RT=100 Ω                 |            |            |       |       |

| voltage        |                        |                          |            |            |       |       |

| Change of Vod  | $\Delta  \mathrm{Vod}$ |                          | $\searrow$ | $\searrow$ | 50    | mV    |

| between High   |                        |                          |            |            |       |       |

| and Low        |                        |                          |            |            |       |       |

| Output         | Vos                    | $(V_{OP}+V_{OM})/2$      | 1.125      | 1.20       | 1.375 | V     |

| voltage offset |                        | RT=100 Ω                 |            |            |       |       |

| Change of Vos  | $\Delta \mathrm{Vos}$  |                          |            |            | 50    | mV    |

| between H      |                        |                          |            |            |       |       |

| and L          |                        |                          |            |            |       |       |

| Output         | Isa                    | $V_{OD} = 0V$ , shorting |            |            | 24    | mA    |

| short-circuit  |                        | driver output to the     |            |            |       |       |

| current        |                        | GND.                     |            |            |       |       |

| Output         | Isab                   | $V_{OD} = 0V$ , shorting |            |            | 12    | mA    |

| short-circuit  |                        | driver output            |            |            |       |       |

| current        |                        | mutually.                |            |            |       |       |

• Approximate Current and Power Consumption

| Power supply Voltage |     | Approximate current<br>consumption [A] |        | Approximate power<br>consumption [W] |         |

|----------------------|-----|----------------------------------------|--------|--------------------------------------|---------|

|                      | [V] | Standard                               | Max.   | Standard                             | Max.    |

| Vcc                  | 1.2 | 0.1548                                 | 0.2737 | 0.1858                               | 0.3285  |

| VCCAUX <sup>1</sup>  | 3.3 | 0.0213                                 | 0.0236 | 0.0702                               | 0.078   |

| VCCPLL               | 3.3 | 0.0239                                 | 0.0239 | 0.079                                | 0.079   |

| VCCIO0~2,4~7         | 3.3 | 0.0469                                 | 0.0472 | 0.1547                               | 0.1557  |

| VCCIO3               | 2.5 | 0.0307                                 | 0.0307 | 0.07675                              | 0.07675 |

| VCCJ                 | 3.3 | 0.0011                                 | 0.0011 | 0.0037                               | 0.0037  |

1. For the power supply "VCCAUX", a peak of 0.085A may flow at start-up.

#### Refresh Rate

| Item         | Sign | Standard | Units |

|--------------|------|----------|-------|

| Refresh rate |      | 71       | Hz    |

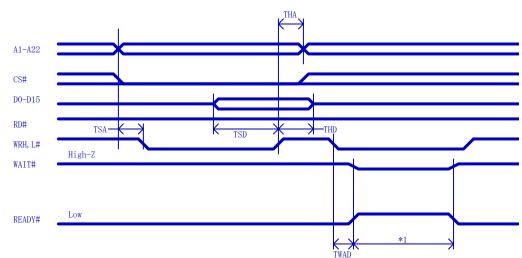

2) Write Cycle for the LCD Controller Host-CPU Interface

| Sign | Item                    | Min. | Max.  | Unit |

|------|-------------------------|------|-------|------|

| TSA  | Address setup           | 10   | —     | ns   |

| THA  | Address hold            | 12   | —     | ns   |

| TSD  | Data setup              | 5    | —     | ns   |

| THD  | Data hold               | 12   | —     | ns   |

| TWAD | WAIT output delay       | —    | 17    | ns   |

| *1   | WAIT# (READY#)<br>width | _    | 11000 | ns   |

WAIT# and READY# signals are outputted under either of the following conditions.

- When the time between the previous write signal rises and the next signal falls is 50 ns or less. (In the case of writing to the Color Palette Register and frame buffer memory.)

- For this LCD controller, write data from the CPU to the frame buffer memory is written to the internal buffer (FIFO). The data written to the FIFO is read from the internal buffer when not reading display data from the frame buffer memory, and is written to the frame buffer.

The internal buffer has room for 1,024 pixels worth of data, but when the write data stored in the internal buffer exceeds the near-full state (data for 1,016 pixels), WAIT# (READY#) is outputted. At this time, when the write speed far exceeds the processing capacity of the LCD controller, the WAIT# (READY#) width becomes longer. However, the maximum values in the above table are only a worst case scenario; in fact, the possibility of it becoming this long is low.

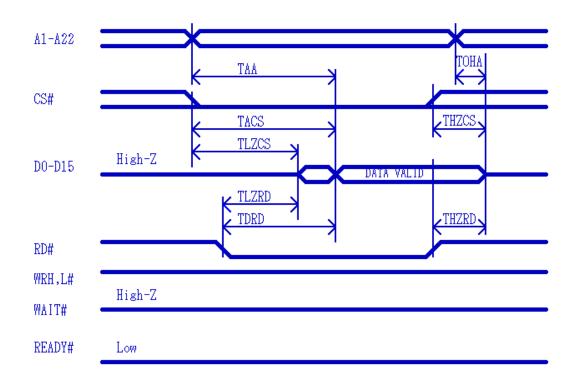

3) Read Cycle for the LCD Controller Host-CPU Interface

| Sign  | Item                                      | Min. | Max. | Unit |

|-------|-------------------------------------------|------|------|------|

| TAA   | Address access time                       |      | 20   | ns   |

| TOHA  | Output hold time                          | 0    | _    | ns   |

| TACS  | Chip select access time                   |      | 15   | ns   |

| TDRD  | Read access time                          |      | 15   | ns   |

| THZRD | Read disable output<br>High-Z time        |      | 15   | ns   |

| TLZRD | Read enable output set time               | 0    | -    | ns   |

| THZCS | Chip select disable<br>output High-Z time |      | 15   | ns   |

| TLZCS | Chip select enable<br>output set time     | 0    |      | ns   |

Caution) The LCD controller can be read only some registers, not be read the frame buffer memory.

4) CPU bus Switching timing of I/O direction

• Image data transfer start time

• Image data transfer finish time

# 6. Address Map

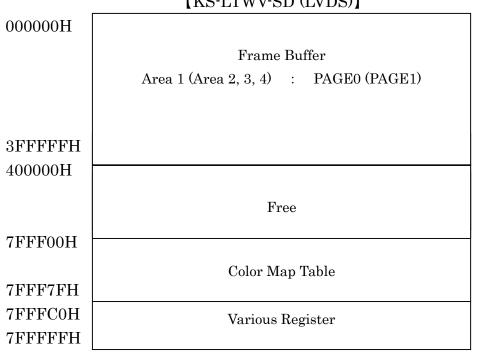

6-1 Address Map for the frame buffer memory

Diagram 6-1 Address Map for the frame buffer memory

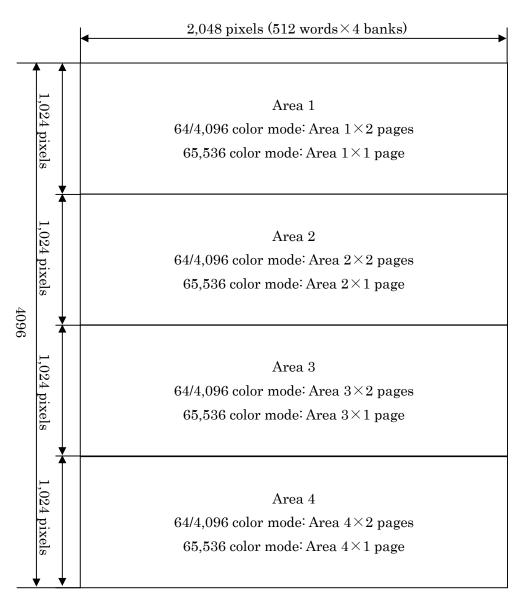

The LCD controller is compatible with an SDR SDRAM of 4,096\*512 words \*4 banks. As in Diagram 6-1, the frame buffer memory is divided into four areas, with a screen resolution of 2,048 pixels (horizontal), 1,024 pixels (vertical) per area. With display and write area specified registers, the area that is displayed to the LCD and the area where the drawing data is written to can be selected.

In the 64/4,096 color mode, the frame buffer has room for 2 pages per area.

With this, two-layer superimposed display (transparent display) within the same area is possible. In the 65,536 color mode, it becomes 1 page per area.

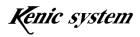

In addition, with the Display-start X-coordinate-setting Register and the Display-start Y-coordinate-setting Register, an image of 800\*600 (SVGA) can be displayed from an arbitrary position in the area as shown in Diagram 6-2.

Diagram 6-2 Display Area

6-2 Address Map for the LCD controller

[KS-LTWV-SD (LVDS)]

The above is the address map for the LCD controller as viewed from the CPU. In 64 colors in 4,096 color mode, the frame buffer has 4 areas for 2 pages (PAGE0 and PAGE1). And, in 65,536 color mode, it has 4 areas.

The bank switching method is used to switch pages, and this is accomplished by setting control register 2 (DCR2). And, the area switching is accomplished by setting the register for display area and write area. Therefore, the address range of the frame buffer as viewed from the CPU is for one area.

# 7. Pixel Composition of the Screen

(1) 64 Colors in 4,096 Color Mode

In the 64 colors in 4,096 color mode, word access and/or byte access is possible.

For word access, set valid data in the lower byte of the 2 bytes from the address in the following diagram, and access the LCD controller. The data for the higher byte is ignored in the LCD controller.

Additionally, when conducting byte access, add one (+1) to the address in the following diagram, and access the LCD controller with an odd-numbered address.

```

(0,0)=0000H, (1,0)=0002H ... ... (2047,0)=0FFEH

(0,1)=1000H, (1,1)=1002H ... ... (2047,1)=1FFEH

(0,2)=2000H, (1,2)=2002H ... ... (2047,2)=2FFEH

(0,1023)=3FF000H, (1,1023)=3FF002H ... ... (2047,1023)=3FFFFEH

```

Each pixel corresponds completely to each bit.

For this LCD controller, the frame buffer exists from (0, 0) to (2,047, 1,023) per area. However, the displayable area range is 800\*480 beginning at the display start coordinate (coordinates set in the Display-start X-coordinate-setting Register and the Display-start Y-coordinate-setting Register.).

(2) 65,536 color mode

| (0,0)=0000H, (1,0)=0002H          | (2047,0)=0FFEH        |

|-----------------------------------|-----------------------|

| (0,1)=1000H, (1,1)=1002H          | (2047,1)=1FFEH        |

| (0,2)=2000H, (1,2)=2002H          | (2047,2)=2FFEH        |

|                                   |                       |

|                                   |                       |

| (0,1023)=3FF000H, (1,1023)=3FF002 | H (2047,1023)=3FFFFEH |

Each pixel corresponds completely to each bit.

For this LCD controller, the frame buffer exists from (0, 0) to (2,047, 1,023) per area. However, the displayable area range is 800\*480 beginning at the display start coordinate (coordinates set in the Display-start X-coordinate-setting Register and the Display-start Y-coordinate-setting Register.).

# 8. Displayed Data

This LCD controller uses the color palette format. Firstly, the following is an explanation of this color palette format.

[About the color palette]

When displaying color, usually the color code is designated; for example, there are times when this color code is fixed, such as 02H for blue, 0CH for green, however, another method is when the value of 02H is not fixed to a color such as red but instead indicates that a value representing a color is being stored at that location. With this way, programmers can code more abstract software.

As such, the register housing the list of color addresses and the colors themselves is called the "color palette table."

For example, let's suppose the command "draw a BOX from (100, 100) to (200, 200) using color 03H" is written in the C language. The color indicated by 03H is at first aqua, but let's also say that afterwards we want to change the color to light green. In this case, we only have to change the color registered to 03H in the color palette, and the areas drawn using 03H will all change automatically. Even when the LCD can display only 64 colors, it is possible to select from 4,096 colors, allowing for a remarkably better visual quality.

(1) 64 Colors in 4,096 Color Mode

The displayed data to be written in each frame buffer need to have a set color palette code.

The access to the frame buffer is possible for both word access and byte access.

When writing data in word access, specify an even-numbered address for access. At this time, the data for the lower byte is valid.

When writing data in byte access, specify an odd-numbered address and access only the lower address.

### Image Memory Area

| 000000H <sup>2</sup> | 000000H~3FFFFEH (Higher bytes D15~8) |    |    |    |    |    |   |   |  |  |  |

|----------------------|--------------------------------------|----|----|----|----|----|---|---|--|--|--|

| Bit                  | 15                                   | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

| Name                 | -                                    | -  | -  | -  | -  | -  | - | - |  |  |  |

| R/W                  | W                                    | W  | W  | W  | W  | W  | W | W |  |  |  |

| Initial              | -                                    | -  | -  | -  | -  | -  | - | - |  |  |  |

| value                |                                      |    |    |    |    |    |   |   |  |  |  |

000000H~3FFFFEH (Higher bytes D15~8)

(Caution) Initial value is indefinite.

#### Image Memory Area

#### 000001H~3FFFFFH (Lower bytes D7~0)

| Bit              | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------------------|----|----|----|----|----|----|----|----|

| Name             | M1 | M0 | P5 | P4 | P3 | P2 | P1 | P0 |

| R/W              | W  | W  | W  | W  | W  | W  | W  | W  |

| Initial<br>value | -  | -  | -  | -  | -  | -  | -  | -  |

(Caution) Initial value is indefinite.

#### Pixel Control Bit bits 7~6

| M1 | M0 | Explanation           |  |  |  |  |  |

|----|----|-----------------------|--|--|--|--|--|

| 0  | 0  | Normal display.       |  |  |  |  |  |

| 0  | 1  | Transmission display. |  |  |  |  |  |

| 1  | 0  | Blink 1.              |  |  |  |  |  |

| 1  | 1  | Blink 2.              |  |  |  |  |  |

(Caution) These M1 and M0 bits function as part of a set with control register 1 (DCR).

#### Color Palette Table bits 5~0

| P5 | P4 | P4 | P2 | P1 | P0 | Explanation                                             |

|----|----|----|----|----|----|---------------------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | The data housed in color map table 0~63 is displayed in |

| 0  | 0  | 0  | 0  | 0  | 1  | advance.                                                |

|    |    |    |    |    |    |                                                         |

| 1  | 1  | 1  | 1  | 1  | 0  |                                                         |

| 1  | 1  | 1  | 1  | 1  | 1  |                                                         |

For the method to house color data for each color palette, refer to the "12. About the Registers" chapter.

(2) 65,536 color mode

With the 65,536 color mode for DCR1, write 16-bit (RGB) data to the frame buffer memory in the following format.

Execute access to the frame buffer using only word access.

Per-byte access is not supported.

### Image Memory Area

### 000000H~3FFFFEH (Higher bytes D15~8)

|         |    | , ε | , , |    |    |    |    |    |

|---------|----|-----|-----|----|----|----|----|----|

| Bit     | 15 | 14  | 13  | 12 | 11 | 10 | 9  | 8  |

| Name    | R4 | R3  | R2  | R1 | R0 | G5 | G4 | G3 |

| R/W     | W  | W   | W   | W  | W  | W  | W  | W  |

| Initial | -  | -   | -   | -  | -  | -  | -  | -  |

| value   |    |     |     |    |    |    |    |    |

Image Memory Area

000001H~3FFFFH (Lower bytes D7~0)

| Bit              | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------------------|----|----|----|----|----|----|----|----|

| Name             | G2 | G1 | G0 | B4 | B3 | B2 | B1 | B0 |

| R/W              | W  | W  | W  | W  | W  | W  | W  | W  |

| Initial<br>value | -  | -  | -  | -  | -  | -  | -  | -  |

## 9. Drawing Function

This LCD controller includes the following drawing functions.

- (1) Line Drawing Function

- (2) Arbitrary Rectangle Fill-in Function

### 9-1 Line Drawing Function

By using this function, arbitrary lines (vertical, horizontal, and diagonal) can be drawn at high-speed.

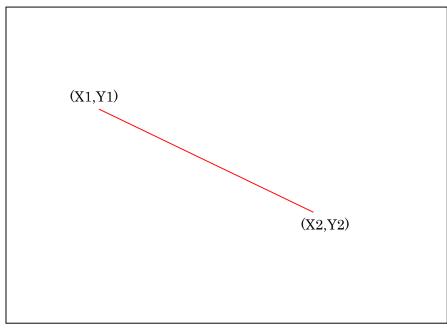

When drawing a line as in Diagram 9-1, after setting the starting point coordinates (X1, Y1), the ending point coordinates (X2, Y2), and the color to the register (Regarding registers, refer to "11. About the Registers".), the line drawing function is performed in the Line-drawing Start-setting Register.

As the size comparison of the starting and ending point coordinates is executed inside the LCD controller, for the Host-CPU side software, register settings can be conducted without worrying about the size comparison. Also, the coordinate register is 2 bytes. When setting a value larger than the area size  $(2,048 \times 1,024 \text{ pixels})$ , beware that the display can become strange.

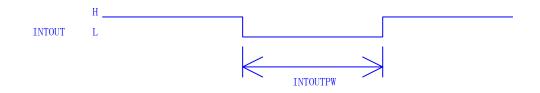

During the line drawing process, avoid accessing the frame buffer memory from the CPU, performing other drawing functions (Hard Fill, Arbitrary Rectangle Fill-in Function, Image Data Transfer Function), or line drawing. During the line drawing process, place a BUSY flag of the Hard Fill Status Register. Check for this flag and confirm that the operation has completed before accessing the frame buffer memory or executing the next drawing function. Additionally, at the completion of the operation, a one-shot signal of the ACTIVE LOW is outputted from the INTOUT signal of the LCD controller (The pulse width is about 1µSEC.). By connecting this signal to the IRQ port of the CPU, the CPU can detect the completion of the operation by interruption.

In the 64/4,096 color mode, the drawing is performed in the display area and write area specified in the write area-specified register, and in a page specified for the DCR2 register.

In the 65,536 color mode, the data is written to the displayed area and the write area specified in the write area-specified register.

Diagram 9-1 About Line Drawing

### 9-2 Arbitrary Rectangle Fill-in Function

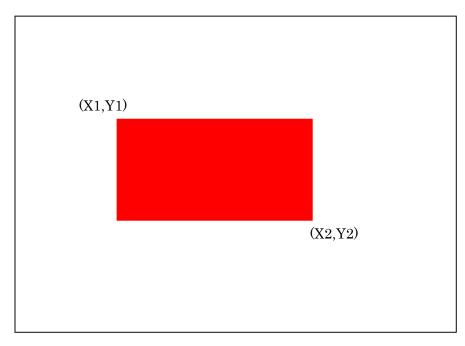

By using this function, arbitrary rectangle fill-in can be drawn at high-speed.

When drawing a rectangle fill-in as in Diagram 9-2, after setting the starting point coordinates (X1, Y1), the ending point coordinates (X2, Y2), and the color to the register (Regarding registers, refer to "12. About the Registers".), the rectangle fill-in function is performed in the Rectangle Fill-in Start Register.

As the size comparison of the starting and ending point coordinates is executed inside the LCD controller, for the Host-CPU side software, register settings can be conducted without worrying about the size comparison. Also, the coordinate register is 2 bytes. When setting a value larger than the area size  $(2,048 \times 1,024 \text{ pixels})$ , beware that the display can become strange, it will take time before the drawing completes.

During the rectangle fill-in process, avoid accessing the frame buffer memory from the CPU, performing other drawing functions (Hard Fill, Line Drawing Function, Image Data Transfer Function), or rectangle fill-in. During the rectangle fill-in process, place a BUSY flag of the Hard Fill Status Register. Check for this flag and confirm that the operation has completed before accessing the frame buffer memory or executing the next drawing function. Additionally, at the completion of the operation, a one-shot signal of the ACTIVE LOW is outputted from the INTOUT signal of the LCD controller (The pulse width is about 1µSEC.). By connecting this signal to the IRQ port of the CPU, the CPU can detect the completion of the operation by interruption.

Diagram 9-2 About Rectangle Fill-in

In the 64/4,096 color mode, the drawing is performed in the display area and write area specified in the write area-specified register, and in a page specified for the DCR2 register.

In the 65,536 color mode, the data is written to the displayed area and the write area specified in the write area-specified register.

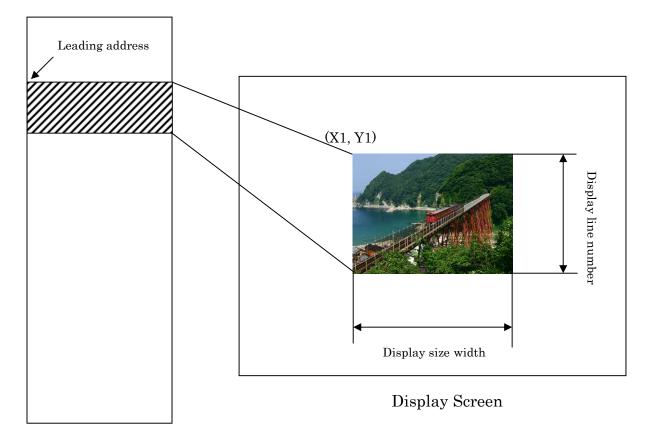

# 10. Image Data Transfer Function

The "Image Data Transfer Function" is a function that reads arbitrary image data from the FROM for images connected to the CPU, writes to the frame buffer, and displays an image on arbitrary coordinates. The LCD controller outputs the bus release signal to the CPU in order to read the data from the FROM for images connected to the CPU, and then checks the release of the bus before reading image data from the FROM for images. Therefore, the CPU is unable to access the external bus during this time.

Only necessary information has to be set in the following registers for the LCD controller to transfer image data automatically (Regarding registers, refer to "12. About the Registers.").

- Image-display Start-position X-coordinate-setting Register

- Image-display Start-position Y-coordinate-setting Register

- Leading-address-setting Register for the Image Data Storage Location

- Image-data Display-size Width-setting Register

- Image-data Display-size Line-number-setting Register

- Image Control Register

For example, when displaying image data stored in the FROM for images to the display coordinates (X1, Y1) as shown in Diagram 10-1, set the address where the data is the leading image stored in Leading-address-setting Register for the Image Data Storage Location, and set the display coordinates (X1, Y1) in the Image-display Start-position X-coordinate-setting Register and the Image-display Start-position Y-coordinate-setting Register. Next, set the display size of the image data (width, line number) in the Image-data Display-size Width-setting and Image-data Register the Display-size Line-number-setting Register. When executing the transfer in the Image Control Register, the LCD controller transfers the image data automatically, and the display is performed. While transferring image data, the CPU is unable to use the external bus.

After completing the transfer, the LCD controller stops the bus open

command to the CPU, and a one-shot signal of the ACTIVE LOW is outputted from the INTOUT pin (The pulse width is about 1 $\mu$ SEC.). Connect this signal to the IRQ port of the CPU; confirm the completion of the transfer before the CPU accesses the external bus.

In addition, use this function in the 65,536 color mode, as the displayed colors become strange when operating in the 64/4,096 color mode.

Image data is written to the displayed area and the write area specified in the write-area-specified register.

FROM for images

Diagram 10-1 Image Data Transfer Image

10-1 Accessing the FROM for images

When the image data transfer is stopped, it is possible to access the FROM for images from the CPU, and image data can be written. For the amount of image data that can be stored in the FROM for images when its capacity is 64Mbytes (512Mbits), with a QVGA (320\*240 pixels) image the size is as follows:

$320^{\star}240^{\star}2Bytes \!=\! 153.6 kBytes$

Therefore, in the FROM for images, the following number of images can be saved.

64Mbytes/153.6kBytes=about 416 images

In VGA size (640\*480 pixels),

640\*480\*2 Bytes=614.4kBytes

Thus, in the FROM for images, the following number of images can be saved.

64Mbytes/614.4kBytes=about 104 images

The LCD controller provides 3-bit output pins A24~A22: FA24 (No.206 pin), FA23 (No. 207 pin), and FA22 (No. 1 pin). As these pins are output pins, avoid connecting to the address signal line from the CPU. Connect to the address pin of the FROM for images from this pin. The 3-bit signal of A24~A22 outputs the contents of the FROM for images address register as-is.

10-2 Transfer Time of Image Data and Video Speed

The time required to read an image with the dimensions of 320\*240 from the FROM for images and write to the frame buffer memory is as follows.

$320 \times 240 \times 182.5$  nsec = 14.02 msec

Therefore, video playback of 30 frames per second (about 33.3 msec cycle) is possible.

However, pixel size is 320\*240, when screen is refreshed by using the method of 10-3, it is refreshed every two frames. As the VSYNC cycle is about 14.1 msec, it becomes a video playback of about 35 frames per second (= $2\times14.1$  msec per frame) in practice.

Moreover, for the dimensions of 640\*480 (in case of VGA size),

$640 \times 480 \times 182.5$  nsec = 56.06 msec

Therefore, video playback of 15 frames per second (about 66.7msec cycle) is possible.

However, when screen is refreshed by using the method of 10-3, as the VSYNC cycle is about 14.1 msec, it becomes a video playback of about 14 frames per second ( $=5 \times 14.1$  msec per frame) in practice.

10-3 About Video

By using the following method (Example: Image size is 640\*480, when screen is refreshed at 14 frames per second), video can be played back smoothly.

- (1) Connect the VSYNC signal outputted from the LCD controller to the interrupt pin input of the CPU.

- (2) Fill in an area (area 1, 2) with hard fill in a single color.

- (3) If VSYNC interruption is detected, make area 1 the write area and area 2 the display area, and transfer the first image.

- (4) With VSYNC interruption, after 5 frames (1 frame: about 14.1msec),

make area 1 the display area and area 2 the write area, and transfer the next image.

At this time, the image transferred in (3) is displayed.

(5) With VSYNC interruption, after 5 frames (1 frame: about 14.1msec), make area 1 the write area and area 2 the display area, and transfer the next image.

At this time, the image transferred in (4) is displayed.

- (6) Smooth animation can be performed by repeating (4) and (5).

- 10-4 During Image Data Transfer

While transferring image data, the CPU bus is released, and because the LCD controller takes over the CPU bus, the CPU is unable to access the external bus during the transfer.

In addition, be aware that depending on the CPU type, there are those which practically stop processing during the bus release.

10-5 Transparency Function of Image Data

When writing image data as shown in Diagram 10-2 to the frame buffer memory (SDRAM), the Image Data Transparency Function can allow only the image data for the aqua-colored area to be written and, on the other hand, prevent the red area from being written. In this way, the background data written to the frame buffer memory can be kept while writing and displaying only the foreground image.

Diagram 10-2 Image Data

By only setting the necessary information in the following registers, (Regarding registers, refer to "12. About the Registers".), the above function can be used.

- Image Data Transparency Function Active/Inactive Register

- Image Data Transparency Color Specified Register

# 11. Self-refresh Function

This LCD controller includes a function to switch the SDRAM to a self-refresh state and thereby cut electric power consumption. The setting for changing the SDRAM to the self-refresh state is performed in the following registers. (Regarding registers, refer to "12. About the Registers".)

• Control Register 3 (DCR3)

In the normal state, when the SELFREF bit of the above register is set to "1", the SDRAM shifts to the self-refresh state. At this time, the display becomes pitch-black. Conversely, in the self-refresh state, when the SELFREF bit of the above register is set to "0", the normal state is restored and the screen is displayed.

Precautions:

- In the self-refresh state, the SDRAM (read and write operations) is not accessed. Therefore, in the self-refresh state, avoid hard fill, line drawing, rectangle drawing, image data transfer, and writing image data from the CPU.

- Additionally, avoid changing to the self-refresh state while performing the hard fill, line drawing, and rectangle drawing functions.

# 12. About the Registers

(1) Register for the Color Palette

Addresses 7FFF00H~7FFF7FH

There are 64 color palettes, and each can be set as 12-bit (4,096 colors). The palette number must be set for drawing.

The write to the color palette register is possible for both in units of byte and word. In word access, the higher side of the data bus is  $G3\sim0$ ,  $B3\sim0$ , the lower side of the data bus is  $R3\sim0$ .

| 00101      |                 |                 |    |                    | -   | -  |    |    |    |    |         |      |      |    |    |    |  |  |

|------------|-----------------|-----------------|----|--------------------|-----|----|----|----|----|----|---------|------|------|----|----|----|--|--|

| Bit order  | b7              | b6              | b5 | b4                 | b3  | b2 | b1 | b0 | b7 | b6 | b5      | b4   | b3   | b2 | b1 | b0 |  |  |

| Color data | -               | -               | -  | -                  | R   | R  | R  | R  | G  | G  | G       | G    | B    | В  | В  | B  |  |  |

| format     |                 |                 |    |                    | 3   | 2  | 1  | 0  | 3  | 2  | 1       | 0    | 3    | 2  | 1  | 0  |  |  |

| Palette 0  |                 | 7FFF01H 7FFF00H |    |                    |     |    |    |    |    |    |         |      |      |    |    |    |  |  |

| Palette 1  |                 | 7FFF03H 7       |    |                    |     |    |    |    |    |    |         | 7FFI | F02I | I  |    |    |  |  |

| Palette 2  |                 | 7FFF05H         |    |                    |     |    |    |    |    |    | 7FFF04H |      |      |    |    |    |  |  |

|            | •               |                 |    |                    |     |    |    |    |    |    |         |      |      |    |    |    |  |  |

|            |                 |                 |    |                    |     |    | •  |    |    |    |         |      |      |    |    |    |  |  |

|            |                 |                 |    |                    |     |    | •  |    |    |    |         |      |      |    |    |    |  |  |

|            |                 |                 |    |                    |     |    | •  |    |    |    |         |      |      |    |    |    |  |  |

| Palette 61 |                 |                 | 7  | FFF                | 7RF | 1  |    |    |    |    | -       | 7FFF | 7741 | Ŧ  |    |    |  |  |

| Palette 62 |                 |                 |    | 7FFF7AH<br>7FFF7CH |     |    |    |    |    |    |         |      |      |    |    |    |  |  |

|            |                 |                 |    | 'FFF               |     |    |    |    |    |    |         |      |      |    |    |    |  |  |

| Palette 63 | 7FFF7FH 7FFF7EH |                 |    |                    |     |    |    |    |    |    |         |      |      |    |    |    |  |  |

#### Example) Color Palette 63

| A | ddress           | 7FFF | 7EH (Ev | en Addr | ess G, | B) |    |    |    |

|---|------------------|------|---------|---------|--------|----|----|----|----|

|   | Bit              | 7    | 6       | 5       | 4      | 3  | 2  | 1  | 0  |

|   | Name             | G3   | G2      | G1      | GO     | B3 | B2 | B1 | BO |

| ĺ | R/W              | W    | W       | ₩       | ₩      | W  | W  | W  | W  |

|   | Initial<br>value | -    | -       | -       | I      | -  | I  | I  | -  |

Address 7FFF7FH (Odd Address R)

| Bit              | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|------------------|---|---|---|---|----|----|----|----|

| Name             |   |   |   |   | R3 | R2 | R1 | RO |

| R/W              | W | ₩ | W | ₩ | W  | W  | W  | W  |

| Initial<br>value | - | - | - | - | -  | -  | -  | -  |

(2) FROM for Images Address Register (For bank switching)

| 1 Iuui 000 | 11110 | 011 |          |      |      |   |   |   |

|------------|-------|-----|----------|------|------|---|---|---|

| Bit        | 7     | 6   | <b>5</b> | 4    | 3    | 2 | 1 | 0 |

| Name       | —     | _   | FA24     | FA23 | FA22 |   | _ | _ |

| R/W        | W     | W   | W        | W    | W    | W | W | W |

| Initial    | 0     | 0   | 0        | 0    | 0    | 0 | 0 | 0 |

| value      |       |     |          |      |      |   |   |   |

Address 7FFFC0H

Use this register when accessing a high-capacity (512Mbit) FROM for images from the CPU and the high-order bit address of the CPU is insufficient.

Bit information set to bits 5, 4, 3 of this register is outputted from the No. 206, 207 and No.1 pins of the LCD controller.

The register can be written to by byte or word access. For word access, set the data in the high-order byte  $(D15\sim8)$ .

(3) Image-display Start-position X-coordinate-setting Register

| Address | ITTTU | $2\Pi$ |    |    |    |       |      |      |

|---------|-------|--------|----|----|----|-------|------|------|

| Bit     | 15    | 14     | 13 | 12 | 11 | 10    | 9    | 8    |

| Name    | -     | -      | -  | -  | -  | X(10) | X(9) | X(8) |

| R/W     | -     | -      | -  | -  | -  | W     | W    | W    |

| Initial | -     | -      | -  | -  | -  | 0     | 0    | 0    |

| value   |       |        |    |    |    |       |      |      |

Address 7FFFC2H

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | X(7) | X(6) | X(5) | X(4) | X(3) | X(2) | X(1) | X(0) |

| R/W     | W    | W    | W    | W    | W    | W    | W    | W    |

| Initial | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| value   |      |      |      |      |      |      |      |      |

This register sets the X-coordinate of the image display starting point. The setting range is  $0\sim2,047$ .

The limit is not applied on the LCD controller side.

The register can be written to by byte or word access.

(4) Image-display Start-position Y-coordinate-setting Register

| 11001000 | 11110 | 111 |    |    |    |    |      |      |

|----------|-------|-----|----|----|----|----|------|------|

| Bit      | 15    | 14  | 13 | 12 | 11 | 10 | 9    | 8    |

| Name     | -     | -   | -  | -  | -  | -  | Y(9) | Y(8) |

| R/W      | -     | -   | -  | -  | -  | -  | W    | W    |

| Initial  | -     | -   | -  | -  | -  | -  | 0    | 0    |

| value    |       |     |    |    |    |    |      |      |

#### Address 7FFFC4H

#### Address 7FFFC5H

| Bit              | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------------|------|------|------|------|------|------|------|------|

| Name             | Y(7) | Y(6) | Y(5) | Y(4) | Y(3) | Y(2) | Y(1) | Y(0) |

| R/W              | W    | W    | W    | W    | W    | W    | W    | W    |

| Initial<br>value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

This register sets the Y-coordinate of the image display starting point. The setting range is  $0\sim1,023$ .

The limit is not applied on the FPGA side.

The register can be written to by byte or word access.

(5) Leading-address-setting Register for the Image Data Storage Location

| Auuress | 111100 | .1 |    |    |    |    |   |        |

|---------|--------|----|----|----|----|----|---|--------|

| Bit     | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8      |

| Name    | -      | -  | -  | -  | -  | -  | - | FA(24) |

| R/W     | -      | -  | -  | -  | -  | -  | - | W      |

| Initial | -      | -  | -  | -  | -  | -  | - | 0      |

| value   |        |    |    |    |    |    |   |        |

#### Address 7FFFC6H

#### Address 7FFFC7H

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name    | FA(23) | FA(22) | FA(21) | FA(20) | FA(19) | FA(18) | FA(17) | FA(16) |

| R/W     | W      | W      | W      | W      | W      | W      | W      | W      |

| Initial | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| value   |        |        |        |        |        |        |        |        |

Address 7FFFC8H

| 11441055 | 1111001 |        |        |        |        |        |       |       |

|----------|---------|--------|--------|--------|--------|--------|-------|-------|

| Bit      | 15      | 14     | 13     | 12     | 11     | 10     | 9     | 8     |

| Name     | FA(15)  | FA(14) | FA(13) | FA(12) | FA(11) | FA(10) | FA(9) | FA(8) |

| R/W      | W       | W      | W      | W      | W      | W      | W     | W     |

| Initial  | 0       | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| value    |         |        |        |        |        |        |       |       |

#### Address 7FFFC9H

| Bit     | 7     | 6     | <b>5</b> | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|----------|-------|-------|-------|-------|-------|

| Name    | FA(7) | FA(6) | FA(5)    | FA(4) | FA(3) | FA(2) | FA(1) | FA(0) |

| R/W     | W     | W     | W        | W     | W     | W     | W     | W     |

| Initial | 0     | 0     | 0        | 0     | 0     | 0     | 0     | 0     |

| value   |       |       |          |       |       |       |       |       |

This register sets the leading address of the FROM where image data is stored. The setting range is 0H~01FFFFFH.

The register can be written to by byte or word access. In word access, write using two steps: "7FFFC6H  $\sim$  7FFFC7H" and "7FFFC8H  $\sim$  7FFFC9H".

(6) Image-data Display-size Width-setting Register

| Address | ITTTU. | AII |    |    |        |        |       |       |

|---------|--------|-----|----|----|--------|--------|-------|-------|

| Bit     | 15     | 14  | 13 | 12 | 11     | 10     | 9     | 8     |

| Name    | -      | -   | -  | -  | XH(11) | XH(10) | XH(9) | XH(8) |

| R/W     | -      | -   | -  | -  | W      | W      | W     | W     |

| Initial | -      | -   | -  | -  | 0      | 0      | 0     | 0     |

| value   |        |     |    |    |        |        |       |       |

## Address 7FFFCAH

#### Address 7FFFCBH

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | XH(7) | XH(6) | XH(5) | XH(4) | XH(3) | XH(2) | XH(1) | XH(0) |

| R/W     | W     | W     | W     | W     | W     | W     | W     | W     |

| Initial | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| value   |       |       |       |       |       |       |       |       |

This register sets the display width of image to display.

The setting range is  $1 \sim 2,048$ .

The limit is not applied on the LCD controller side.

The register can be written to by byte or word access.

# (7) Image-data Display-size Line-number-setting Register

| iiddi coo i |    |    |    |    |    |        |       |       |

|-------------|----|----|----|----|----|--------|-------|-------|

| Bit         | 15 | 14 | 13 | 12 | 11 | 10     | 9     | 8     |

| Name        | -  | -  | -  | -  | -  | YV(10) | YV(9) | YV(8) |

| R/W         | -  | -  | -  | -  | -  | W      | W     | W     |

| Initial     | -  | -  | -  | -  | -  | 0      | 0     | 0     |

| value       |    |    |    |    |    |        |       |       |

#### Address 7FFFCCH

#### Address 7FFFCDH

| Bit              | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name             | YV(7) | YV(6) | YV(5) | YV(4) | YV(3) | YV(2) | YV(1) | YV(0) |

| R/W              | W     | W     | W     | W     | W     | W     | W     | W     |

| Initial<br>value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

This register sets the display line number of image to display.

The setting range is  $1 \sim 1,024$ .

The limit is not applied on the LCD cotroller side.

The register can be written to by byte or word access.

(8) Image Control Register

| 11dd1000 |   |   |   |   |   |   |   |    |  |  |  |  |

|----------|---|---|---|---|---|---|---|----|--|--|--|--|

| Bit      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |  |  |  |  |

| Name     | - | - | - | - | - | - | - | ST |  |  |  |  |

| R/W      | - | - | - | - | - | - | - | W  |  |  |  |  |

| Initial  | - | - | - | - | - | - | - | 0  |  |  |  |  |

| value    |   |   |   |   |   |   |   |    |  |  |  |  |

#### Address 7FFFCEH (Write side)

This register sets the transfer start command for image data.

Bit 0 carries out the start instruction for image data transfer.

| ST | Explanation                                                            |

|----|------------------------------------------------------------------------|

| 1  | Transfer of image data is started.                                     |

| 0  | This is an initial value or is returned to 0 after starting operation. |

When the transfer of image data is completed, a one-shot signal of the

ACTIVE LOW is outputted from the INTOUT signal of the LCD controller. The pulse width is about 1 $\mu$ SEC. With IRQ interruption processing, the CPU side can setup and start transfer of the next image data.

(9) Drawing X-coordinates-starting-point Setting Register

| nuurossi |    | 11 |    |    |    |       |      |      |

|----------|----|----|----|----|----|-------|------|------|

| Bit      | 15 | 14 | 13 | 12 | 11 | 10    | 9    | 8    |

| Name     | -  | -  | -  | -  | -  | X(10) | X(9) | X(8) |

| R/W      | -  | -  | -  | -  | -  | W     | W    | W    |

| Initial  | -  | -  | -  | -  | -  | 0     | 0    | 0    |

| value    |    |    |    |    |    |       |      |      |

#### Address 7FFFD0H

Address 7FFFD1H

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | X(7) | X(6) | X(5) | X(4) | X(3) | X(2) | X(1) | X(0) |

| R/W     | W    | W    | W    | W    | W    | W    | W    | W    |

| Initial | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| value   |      |      |      |      |      |      |      |      |

This register sets the X starting point coordinates of the drawing data. The setting range is  $0\sim 2,047$ .

The limit is not applied on the LCD controller side.

The register can be written to by byte or word access.

It is the same as the Arbitrary Rectangle Fill-in and Line-drawing Functions

(10) Drawing X-coordinates-starting-point Setting Register

| Auuress | $(\Gamma \Gamma \Gamma D 2)$ | 11 |    |    |    |    |      |      |

|---------|------------------------------|----|----|----|----|----|------|------|

| Bit     | 15                           | 14 | 13 | 12 | 11 | 10 | 9    | 8    |

| Name    | -                            | -  | -  | -  | -  | -  | Y(9) | Y(8) |

| R/W     | -                            | -  | -  | -  | -  | -  | W    | W    |

| Initial | -                            | -  | -  | -  | -  | -  | 0    | 0    |

| value   |                              |    |    |    |    |    |      |      |

#### Address 7FFFD2H

Address 7FFFD3H

| iiddi coo i      | _    |      |      |      |      |      |      |      |

|------------------|------|------|------|------|------|------|------|------|

| Bit              | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Name             | Y(7) | Y(6) | Y(5) | Y(4) | Y(3) | Y(2) | Y(1) | Y(0) |

| R/W              | W    | W    | W    | W    | W    | W    | W    | W    |

| Initial<br>value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

This register sets the Y starting point coordinates of the drawing data. The setting range is  $0\sim1,023$ .

The limit is not applied on the LCD controller side.

The register can be written to by byte or word access.

It is the same as the Arbitrary Rectangle Fill-in and Line-drawing Functions.

(11) Drawing X-coordinates-ending-point Setting Register

| Address I | $\mathbf{\Gamma} \mathbf{\Gamma} \mathbf{\Gamma} \mathbf{D} 4$ | LI |    |    |    |       |      |      |

|-----------|----------------------------------------------------------------|----|----|----|----|-------|------|------|

| Bit       | 15                                                             | 14 | 13 | 12 | 11 | 10    | 9    | 8    |

| Name      | -                                                              | -  | -  | -  | -  | X(10) | X(9) | X(8) |

| R/W       | -                                                              | -  | -  | -  | -  | W     | W    | W    |

| Initial   | -                                                              | -  | -  | -  | -  | 0     | 0    | 0    |

| value     |                                                                |    |    |    |    |       |      |      |

# Address 7FFFD4H

# Address 7FFFD5H

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | X(7) | X(6) | X(5) | X(4) | X(3) | X(2) | X(1) | X(0) |

| R/W     | W    | W    | W    | W    | W    | W    | W    | W    |

| Initial | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| value   |      |      |      |      |      |      |      |      |

This register sets the X ending point coordinates of the drawing data.

The setting range is  $0\sim 2,047$ .

The limit is not applied on the LCD controller side.

The register can be written to by byte or word access.

It is the same as the Arbitrary Rectangle Fill-in and Line-drawing Functions.

# (12) Drawing Y-coordinates-ending-point Setting Register

| iluai 000 | <b>IIID</b> 0. |    |    |    |    |    |      |      |

|-----------|----------------|----|----|----|----|----|------|------|

| Bit       | 15             | 14 | 13 | 12 | 11 | 10 | 9    | 8    |