May 2015, First Edition (Japanese version) June 2015, First Edition (English version)

(Note) Silk screen print in the above picture is a composite. The actual print may differ.

#### • Introduction $\bullet$

First of all, thank you for having purchased our command-driven LCD controller IC. (KS-570CT-I1) (the "Product").

This hardware manual (the "Manual") provides an overview of the Product. We hope that you will read the Manual carefully and make use of it for efficient development.

#### Important Information

- The Product and this Manual may change without notice. Before using the Product, obtain the newest catalog, manual,etc., from the company website.

- 2. The Product is not designed to be used in systems or devices that can cause death, injury, or serious physical or environmental damage directly due to any malfunction of the Product (life support device, nuclear facility equipment, aircraft, traffic control equipment, various safety devices, etc.). Danger and damage due to the Product being used in the foregoing systems or devices are the sole responsibility of the customer.

- 3. We assume no responsibility for any damages due to the use or the operation of the Product in a misguided or wrongful way.

- 4. The usage examples outlined herein are only an explanation of the Product functions. We assume no responsibility for any complaints, accidents, or any disadvantages which may be caused by the use on the basis of the examples outlined in this Manual.

# Contents

| 1.  | Product Features and Overview                       | P5  |

|-----|-----------------------------------------------------|-----|

| 2.  | System Configuration Diagram                        | P6  |

| 3.  | Pins                                                | P7  |

| 4.  | Electric Characteristics                            | P12 |

| 5.  | Clock                                               | P20 |

| 6.  | RESET                                               | P23 |

| 7.  | Serial Communication Interface (SCI)                | P26 |

| 8.  | Frame Buffer Memory                                 | P29 |

| 9.  | LCD Interface                                       | P34 |

| 10. | SPI Interface                                       | P37 |

| 11. | Serial Flash Memory                                 | P39 |

| 12. | Touch Panel                                         | P43 |

| 13. | LED Backlight                                       | P53 |

| 14. | Buzzer                                              | P54 |

| 15. | Treatment for Power Pins, Unused Pin and Other Pins |     |

|     |                                                     | P56 |

| 16. | Font Data                                           | P57 |

| 17. | Drawing Functions and Drawing Colors                | P58 |

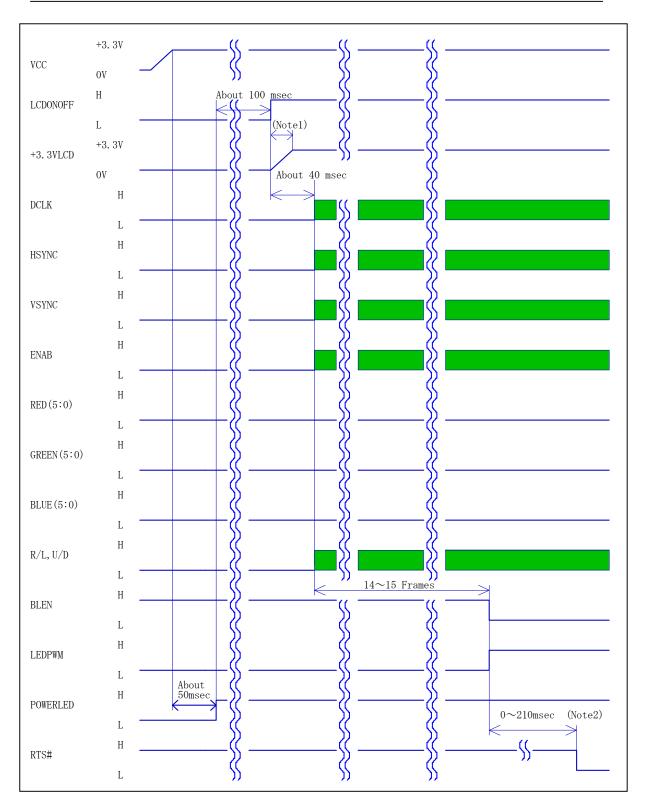

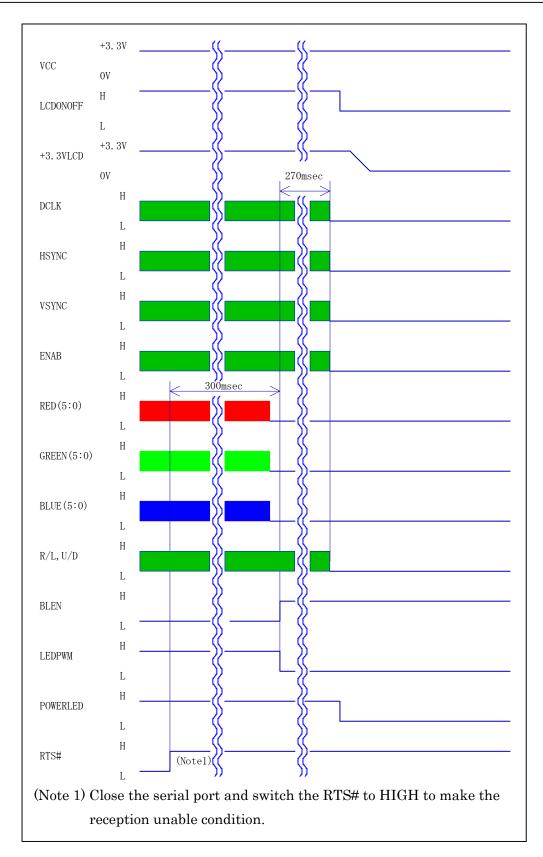

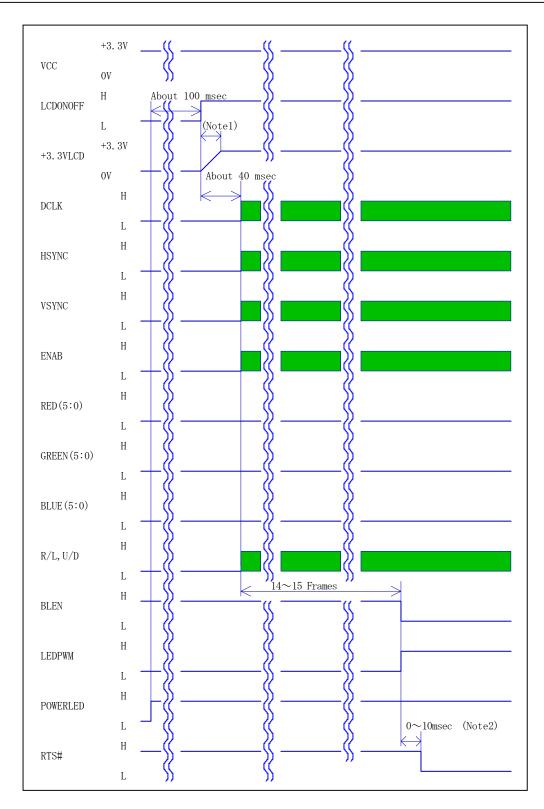

| 18. | Power Supply Sequence and Power Conservation        | P60 |

| 19. | Outline Dimension                                   | P71 |

| 20. | Handling Precautions                                | P72 |

| 21. | <b>Operating Condition Precautions</b>              | P77 |

|     |                                                     |     |

| 22. | Implementation     | P80 |

|-----|--------------------|-----|

| 23. | Reference Circuits | P83 |

### 1. Product Features and Overview

KS-570CT-I1 is an LCD controller that allows one to drive such as drawing dots, straight lines, and rectangles with only RS-232C commands. The controller includes the following features.

- 1) The LCD controller includes drawing functions. The LCD controller allows a user to easily draw with commands transmitted through RS-232C from the user's microcomputer.

- 2) The LCD controller includes a touch panel controller (resolution of 10 bits.)

- The LCD controller allows one to draw a bitmap image on the maximum size of 8,192 bits screen, by connecting to the microSD card.

- 4) The LCD controller includes the 16-dot font data (the half and full size).

- 5) The LCD controller enables one to draw the 24-dot font (the half and full size) characters by writing the 24-dot font data in the serial flash memory.

The 24-dot font data is attached to our starter kit.

- 6) The display color is 65,536 colors.

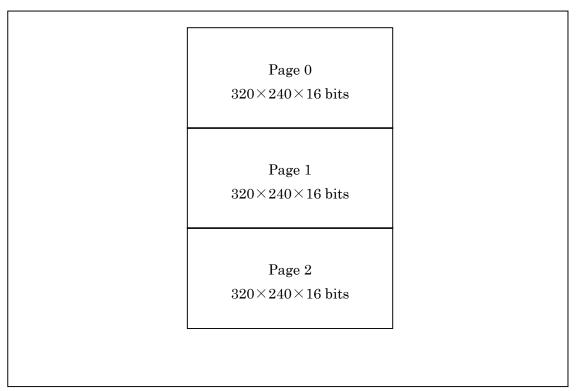

- 7) The display range is 3 pages.

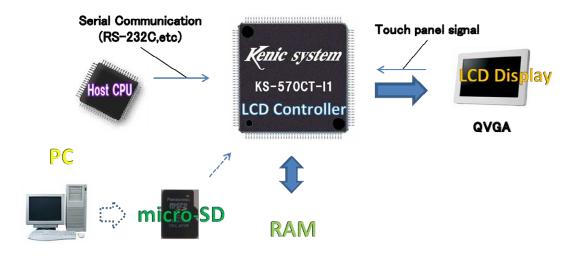

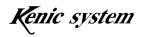

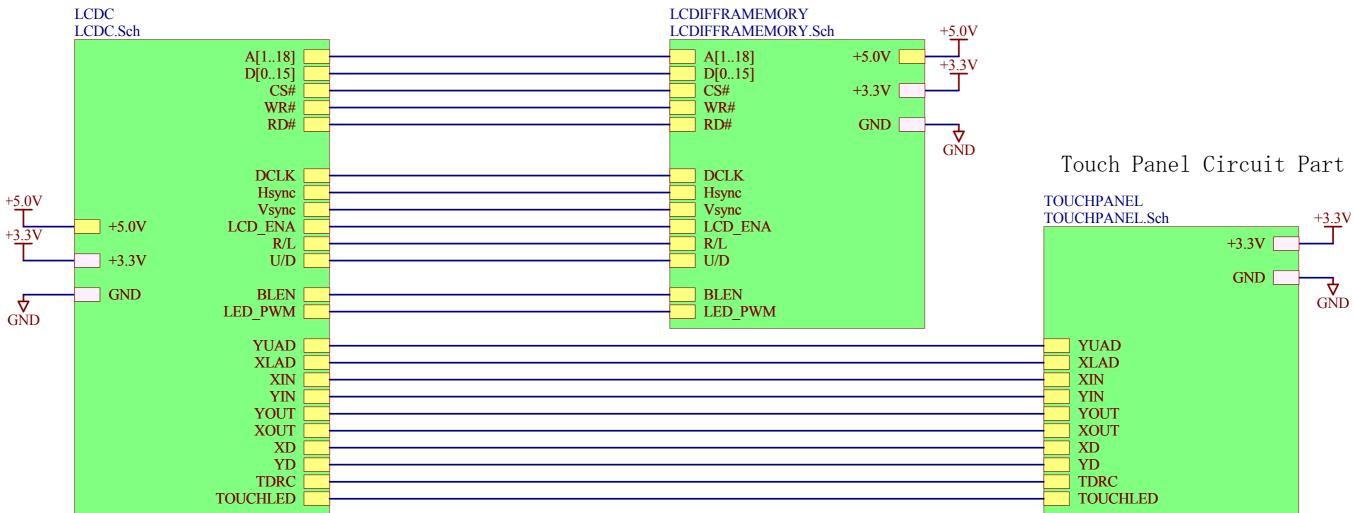

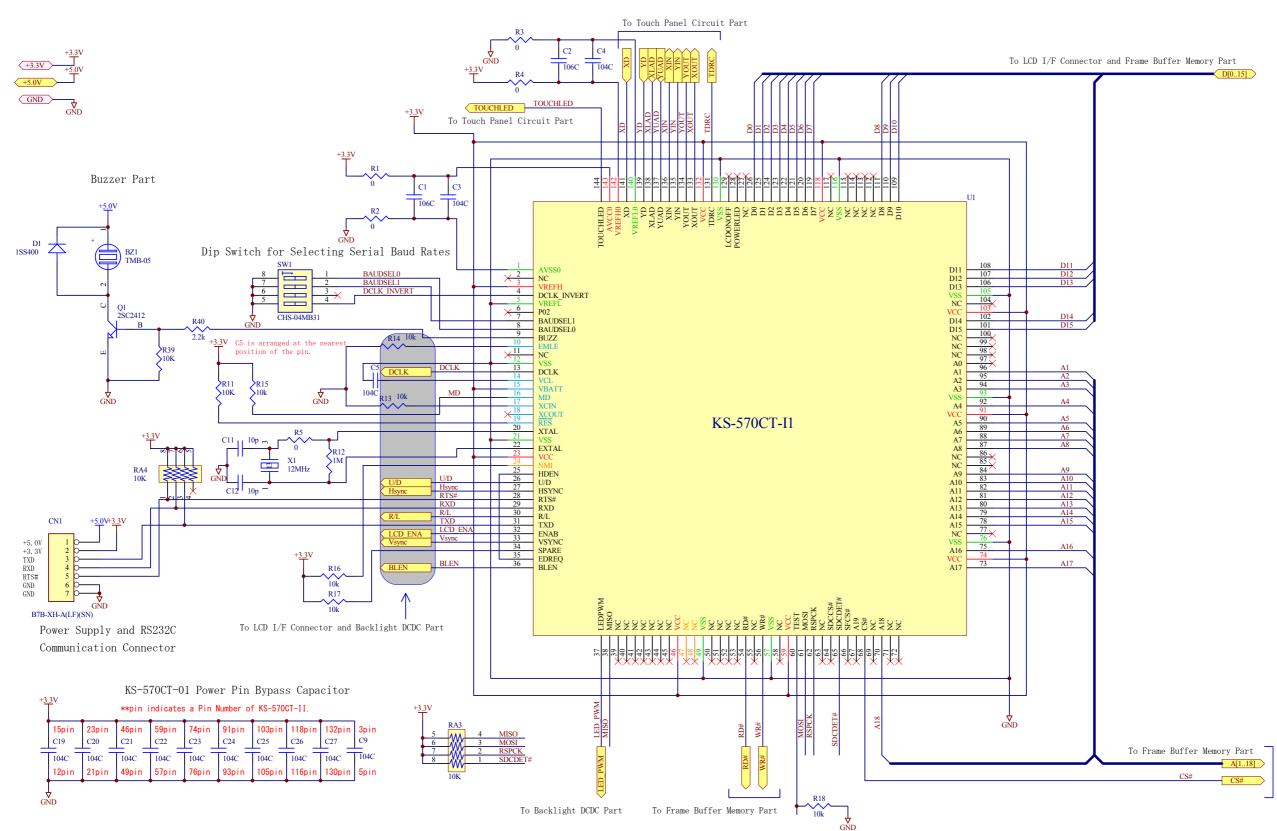

# 2. System Configuration Diagram

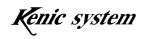

The system configuration of the KS-570CT-I1 is described by Fig. 2-1 below. The LCD controller is completed with a SRAM that is prepared by a user. Furthermore, by connecting the serial flash memory or microSD card, it is also possible to display an image.

Fig. 2-1 Configuration Diagram

### 3. Pins

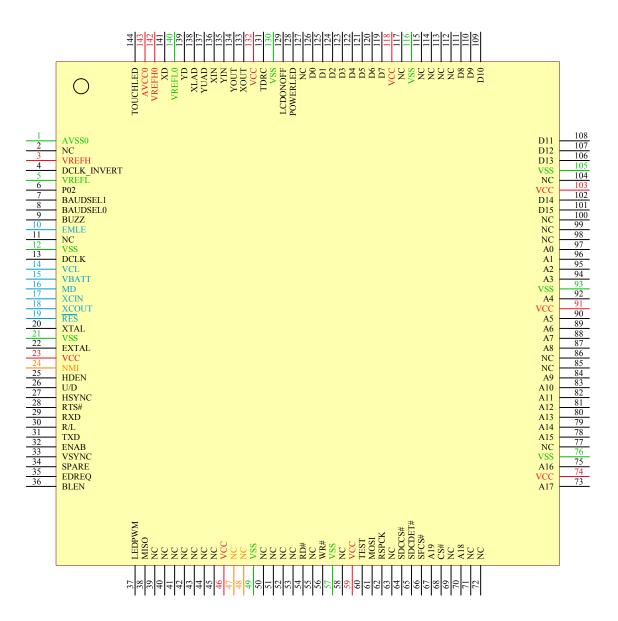

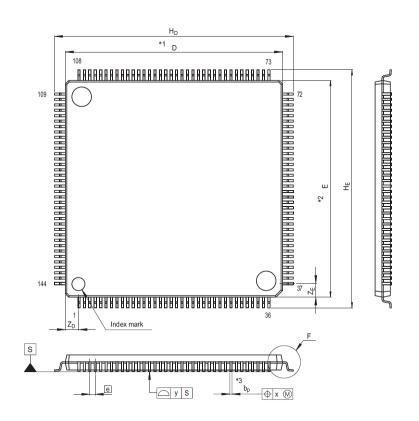

Fig.3-1 shows the pin assignment for KS-570CT-I1.

Fig. 3-1 KS-570CT-I1 Pin assignment

Table 3-1shows the pin assignment table for KS-570CT-I1 (the list of pin numbers and signal names.)

| Pin<br>No | Pin Name        | I/O | PULL<br>MODE | Drive<br>Capab<br>ility | 5V<br>Tolerant | Schmidt<br>Trigger Input | Interface                                               |  |  |

|-----------|-----------------|-----|--------------|-------------------------|----------------|--------------------------|---------------------------------------------------------|--|--|

| 1         | AVSS0           | Ι   | _            | _                       | _              | _                        | 0V (for Analog)                                         |  |  |

| 2         | NC              | 0   | —            | _                       | _              | _                        | No connection                                           |  |  |

| 3         | VREFH           | Ι   | _            | _                       | _              | _                        | +3.3V                                                   |  |  |

| 4         | DCLK_IN<br>VERT | Ι   | Pull-up      |                         |                | 0                        | For DCLK Inverting setting<br>Dip switch etc.           |  |  |

| 5         | VREFL           | Ι   | —            | _                       | _              | _                        | 0V                                                      |  |  |

| 6         | P02             | Ι   | Pull-up      | _                       | _              | 0                        | No connection                                           |  |  |

| 7         | BAUD<br>SEL1    | Ι   | Pull-up      | -                       | _              | 0                        | Dip Switch for setting RS-232C baud                     |  |  |

| 8         | BAUD<br>SEL0    | Ι   | Pull-up      | Ι                       |                | 0                        | rates                                                   |  |  |

| 9         | BUZZ            | 0   | —            | HIGH                    | -              | _                        | Connected to BUZZ                                       |  |  |

| 10        | EMLE            | Ι   | _            | _                       | _              | _                        | 10k Pull-down                                           |  |  |

| 11        | NC              | 0   | _            | _                       | _              | _                        | No connection                                           |  |  |

| 12        | VSS             | Ι   | _            | _                       | _              | _                        | 0V                                                      |  |  |

| 13        | DCLK            | 0   | —            | HIGH                    |                | _                        | To LCD panel                                            |  |  |

| 14        | VCL             | Ι   | —            | _                       |                | _                        | Connected to the capacitor of 0.1uF                     |  |  |

| 15        | VBATT           | Ι   | _            | —                       | _              | _                        | +3.3V                                                   |  |  |

| 16        | MD              | Ι   | _            | _                       | _              | _                        | 10k Pull-up                                             |  |  |

| 17        | XCIN            | Ι   | _            | _                       | _              | _                        | 10k Pull-up                                             |  |  |

| 18        | XCOUT           | 0   | _            | _                       | _              | _                        | No connection                                           |  |  |

| 19        | RES#            | Ι   | _            | _                       | _              | 0                        | 10k Pull-up                                             |  |  |

| 20        | XTAL            | 0   | _            | HIGH                    | _              | _                        | Connected to the crystal oscillator                     |  |  |

| 21        | VSS             | Ι   | _            | _                       | _              | _                        | OV                                                      |  |  |

| 22        | EXTAL           | Ι   | _            | _                       | _              | _                        | Connected to the crystal oscillator                     |  |  |

| 23        | VCC             | I   | _            | _                       | _              | _                        | +3.3V                                                   |  |  |

| 24        | NMI             | I   | _            | _                       | _              | 0                        | 10k Pull-up                                             |  |  |

| 25        | HDEN            | 0   | _            | HIGH                    | _              |                          | Connected the 35th Pin                                  |  |  |

| 26        | U/D             | 0   | _            | HIGH                    | _              | _                        | To LCD panel                                            |  |  |

| 27        | HSYNC           | 0   | _            | HIGH                    | _              | _                        | To LCD panel                                            |  |  |

| 28        | RTS#            | 0   | _            | HIGH                    | _              | _                        | Serial RTS Output                                       |  |  |

| 29        | RXD             | I   | _            | _                       | 0              | 0                        | Serial Receive Data Input                               |  |  |

| 30        | R/L             | 0   | _            | Normal                  | _              |                          | To LCD panel                                            |  |  |

| 31        | TXD             | 0   | _            | HIGH                    | _              | _                        | Serial Transmit Data Output                             |  |  |

| 32        | ENAB            | 0   | _            | HIGH                    | _              | _                        | To LCD panel                                            |  |  |

| 33        | VSYNC           | 0   | _            | HIGH                    | _              |                          | To LCD panel                                            |  |  |

| 34        | SPARE           | I   | _            | _                       | _              | 0                        | 10k Pull-up                                             |  |  |

| 35        | EDREQ           | I   | _            | _                       | _              | -                        | Connected the 25th Pin                                  |  |  |

| 36        | BLEN            | 0   | _            | HIGH                    | _              | _                        | To the LED Backlight I/F part                           |  |  |

| 37        | LED<br>PWM      | 0   | _            | HIGH                    | _              |                          | To the LED Backlight I/F part                           |  |  |

| 38        | MISO            | Ι   | —            | _                       | 0              | _                        | SPI signal: To the Serial Flash Memory,<br>microSD Card |  |  |

| 39        | NC              | 0   | —            |                         |                | -                        | No connection                                           |  |  |

| 40        | NC              | 0   | —            | _                       |                | —                        | No connection                                           |  |  |

| 41        | NC              | 0   | _            | _                       | _              | —                        | No connection                                           |  |  |

Table 3-1 Pin Assignment Table for KS-570CT-I1 (1/4)

-8-

| Pin<br>No       | Pin Name | I/O      | PULL<br>MODE | Drive<br>Capab | 5V<br>Tolerant | Schmidt<br>Trigger Input | Interface                                        |  |

|-----------------|----------|----------|--------------|----------------|----------------|--------------------------|--------------------------------------------------|--|

| 42              | NC       | 0        |              | ility          |                |                          | No connection                                    |  |

| 43              | NC       | 0        | _            | _              | _              |                          | No connection                                    |  |

| 43              | NC       | 0        | _            | _              |                |                          | No connection                                    |  |

| 44              | NC       | -        | _            | _              |                |                          | No connection                                    |  |

|                 | VCC      | 0        |              | _              |                |                          | +3.3V                                            |  |

| $\frac{46}{47}$ | NC       | I<br>I/O | —            |                |                |                          |                                                  |  |

|                 | NC       | -        | _            | _              | _              | _                        | No connection                                    |  |

| 48              | VSS      | I/O      | _            | _              |                |                          | No connection<br>OV                              |  |

| 49              | NC VS5   | I        |              |                |                |                          |                                                  |  |

| 50              | NC<br>NC | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 51              |          | 0        |              | _              |                | _                        | No connection                                    |  |

| 52              | NC       | 0        |              | _              |                | _                        | No connection                                    |  |

| 53              | NC DD#   | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 54              | RD#      | 0        | _            | Normal         | _              |                          | Frame Buffer Memory Control Signal               |  |

| 55              | NC       | 0        | _            | _              | —              | _                        | No connection                                    |  |

| 56              | WR#      | 0        | _            | Normal         | _              | _                        | Frame Buffer Memory Control Signal               |  |

| 57              | VSS      | Ι        | _            | —              | _              | _                        | 0V                                               |  |

| 58              | NC       | 0        | -            | _              | —              | —                        | No connection                                    |  |

| 59              | VCC      | Ι        | —            | —              | _              | _                        | +3.3V                                            |  |

| 60              | TEST     | Ι        | —            | —              | —              | 0                        | 10k Pull-down                                    |  |

| 61              | MOSI     | 0        | _            | HIGH           | _              | _                        | SPI signal: To the Serial Flash Memory,          |  |

| 01              | 1110.01  | Ŭ        |              |                |                |                          | the microSD Card                                 |  |

| 62              | RSPCK    | 0        | _            | HIGH           | _              | _                        | SPI signal: To the Serial Flash Memory,          |  |

| 69              | NC       | 0        | _            | _              | _              | _                        | the microSD Card                                 |  |

| 63              | SDCCS#   | 0        |              |                |                | _                        | No connection<br>SPI signal: To the microSD card |  |

| 64              | SDCCS#   | 0        | _            | HIGH           | _              |                          | SPI signal. To the microSD card                  |  |

| 65              | DET#     | Ι        | —            | _              | —              | $\bigcirc$               | To microSD card                                  |  |

| 66              | SFCS#    | 0        | _            | Normal         | _              | _                        | SPI signal: To the Serial Flash Memory           |  |

| 67              | A19      | 0        | —            | Normal         |                | _                        | No connection                                    |  |

| 68              | CS#      | 0        | _            | HIGH           | _              | _                        | Frame Buffer Memory Control Signal               |  |

| 69              | NC       | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 70              | A18      | 0        | —            | Normal         |                | _                        | Frame Buffer Memory Address Bus                  |  |

| 71              | NC       | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 72              | NC       | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 73              | A17      | 0        | _            | Normal         | _              | _                        | Frame Buffer Memory Address Bus                  |  |

| 74              | VCC      | Ι        | _            | _              | _              | _                        | +3.3V                                            |  |

| 75              | A16      | 0        | _            | Normal         | _              | _                        | Frame Buffer Memory Address Bus                  |  |

| 76              | VSS      | Ι        | _            | _              | _              | _                        | OV                                               |  |

| 77              | NC       | 0        | _            | —              | _              | _                        | No connection                                    |  |

| 78              | A15      | 0        | _            | Normal         | _              | _                        |                                                  |  |

| 79              | A14      | 0        | _            | Normal         | _              | _                        |                                                  |  |

| 80              | A13      | 0        | _            | Normal         | _              |                          | 1                                                |  |

| 81              | A12      | 0        | _            | Normal         | _              |                          | Frame Buffer Memory Address Bus                  |  |

| 82              | A11      | 0        | _            | Normal         | _              |                          | Trance Durier Frenory Hutress Dub                |  |

| 83              | A10      | 0        | _            | Normal         | _              |                          |                                                  |  |

| 84              | A9       | 0        | _            | Normal         | _              |                          | 4                                                |  |

| 85              | NC       | 0        | _            |                | _              | _                        | No connection                                    |  |

| 86              | NC       | 0        | _            | _              | _              | _                        | No connection                                    |  |

| 87              | A8       | 0        | _            | Normal         |                |                          |                                                  |  |

| 88              | Ao<br>A7 | 0        | _            | Normal         |                |                          | Frame Buffer Memory Address Bus                  |  |

| 89              | A6       | 0        | _            | Normal         |                |                          | Frame Duffer Memory Address Dus                  |  |

| 09              | AU       | U        |              | inoimai        |                |                          |                                                  |  |

Table 3-1 Pin Assignment Table for KS-570CT-I1 (2/4)

-9-

| Pin<br>No | Pin Name     | I/O | PULL<br>MODE | Drive<br>Capab<br>ility | 5V<br>Tolerant | Schmidt<br>Trigger Input | Interface                            |

|-----------|--------------|-----|--------------|-------------------------|----------------|--------------------------|--------------------------------------|

| 90        | A5           | 0   | _            | Normal                  |                | -                        | Frame Buffer Memory Address Bus      |

| 91        | VCC          | Ι   | _            | _                       | _              | _                        | +3.3V                                |

| 92        | A4           | 0   | _            | Normal                  | _              | _                        | Frame Buffer Memory Address Bus      |

| 93        | VSS          | Ι   | -            | —                       |                | _                        | 0V                                   |

| 94        | A3           | 0   | _            | Normal                  | _              | _                        |                                      |

| 95        | A2           | 0   | _            | Normal                  | _              | _                        | Frame Buffer Memory Address Bus      |

| 96        | A1           | 0   | _            | Normal                  |                | _                        |                                      |

| 97        | A0           | 0   | -            | Normal                  | -              | _                        | No connection                        |

| 98        | NC           | 0   | _            | _                       | _              | _                        | No connection                        |

| 99        | NC           | 0   | _            | _                       |                | -                        | No connection                        |

| 100       | NC           | 0   | _            | _                       |                | -                        | No connection                        |

| 101       | D15          | I/O | _            | Normal                  | _              | _                        | To the Frame Buffer Memory Data Bus, |

| 102       | D14          | I/O | _            | Normal                  | _              | _                        | and the LCD                          |

| 103       | VCC          | Ι   | -            | —                       | -              | _                        | +3.3V                                |

| 104       | NC           | 0   | _            | —                       | _              | _                        | No connection                        |

| 105       | VSS          | Ι   | _            | _                       | _              | _                        | 0V                                   |

| 106       | D13          | I/O | -            | Normal                  | -              | _                        |                                      |

| 107       | D12          | I/O | _            | Normal                  |                | _                        |                                      |

| 108       | D11          | I/O | _            | Normal                  | _              | _                        | To the Frame Buffer Memory Data Bus, |

| 109       | D10          | I/O | -            | Normal                  |                | _                        | and the LCD                          |

| 110       | D9           | I/O | -            | Normal                  |                | _                        |                                      |

| 111       | D8           | I/O | _            | Normal                  | _              | _                        |                                      |

| 112       | NC           | 0   | -            | —                       | -              | _                        | No connection                        |

| 113       | NC           | 0   | -            | —                       |                | _                        | No connection                        |

| 114       | NC           | 0   | _            | _                       | _              | _                        | No connection                        |

| 115       | NC           | 0   | _            | —                       |                | _                        | No connection                        |

| 116       | VSS          | Ι   | _            | _                       |                | -                        | 0V                                   |

| 117       | NC           | 0   | _            | —                       | _              | _                        | No connection                        |

| 118       | VCC          | Ι   | _            | —                       | _              | _                        | +3.3V                                |

| 119       | D7           | I/O | _            | Normal                  | _              | _                        |                                      |

| 120       | D6           | I/O | _            | Normal                  |                | _                        |                                      |

| 121       | D5           | I/O | _            | Normal                  | _              | _                        |                                      |

| 122       | D4           | I/O | _            | Normal                  | _              | _                        | To the Frame Buffer Memory Data Bus, |

| 123       | D3           | I/O |              | Normal                  |                |                          | and the LCD                          |

| 124       | D2           | I/O |              | Normal                  |                |                          | ]                                    |

| 125       | D1           | I/O | _            | Normal                  | _              | _                        |                                      |

| 126       | D0           | I/O |              | Normal                  |                |                          | ]                                    |

| 127       | NC           | 0   |              | _                       |                |                          | No connection                        |

| 128       | POWER<br>LED | 0   | _            | Normal                  | -              | _                        | LED, and Others                      |

| 129       | LCDON<br>OFF | 0   | _            | Normal                  | _              | _                        | LCD Power Control                    |

| 130       | VSS          | Ι   | _            | _                       | —              | _                        | 0V                                   |

| 131       | TDRC         | 0   | _            | Normal                  | —              | _                        | To the Touch Panel Control Circuit   |

| 132       | VCC          | Ι   | _            | _                       | _              | _                        | +3.3V                                |

| 133       | XOUT         | 0   | _            | Normal                  | _              | _                        |                                      |

| 134       | YOUT         | 0   | _            | Normal                  | _              | _                        | To the Touch Panel Control Circuit   |

Table 3-1 Pin Assignment Table for KS-570CT-I1 (3/4)

|           |              |     |              |                         | 0              |                          |                                            |

|-----------|--------------|-----|--------------|-------------------------|----------------|--------------------------|--------------------------------------------|

| Pin<br>No | Pin Name     | I/O | PULL<br>MODE | Drive<br>Capab<br>ility | 5V<br>Tolerant | Schmidt<br>Trigger Input | Interface                                  |

| 135       | YIN          | 0   | -            | Normal                  | -              | _                        |                                            |

| 136       | XIN          | 0   | -            | Normal                  | -              | _                        |                                            |

| 137       | YUAD         | Ι   | _            | _                       | _              | _                        | To the Touch Panel Control Circuit         |

| 138       | XLAD         | Ι   | -            |                         | -              | _                        |                                            |

| 139       | YD           | Ι   | Pull-up      | _                       | _              | 0                        | Inverting the Touch Panel Data Coordinates |

| 140       | VREFLO       | Ι   | -            |                         | -              | _                        | 0V (for Analog)                            |

| 141       | XD           | Ι   | Pull-up      | —                       | -              | 0                        | Inverting the Touch Panel Data Coordinates |

| 142       | VREFH0       | Ι   | _            | _                       | —              | _                        | +3.3V (for Analog)                         |

| 143       | AVCC0        | Ι   | -            | -                       |                |                          | +3.3V (for Analog)                         |

| 144       | TOUCH<br>LED | 0   | —            | HIGH                    |                | -                        | LED, and Others                            |

Table 3-1 Pin Assignment Table for KS-570CT-I1 (4/4)

(Note 1) Pins that are marked  $\bigcirc$  in the 5V tolerant raw are pins that correspond to the 5V tolerant.

(Note 2) Pins that are marked  $\bigcirc$  in the column of the Schmidt trigger input are the Schmidt trigger input pins.

Input pins other than those above (except for the power pins), and input/output pins are normal pins.

### 4. Electric Characteristics

### 4-1 Absolute Maximum Rating

Table 4-1 Absolute Maximum Rating

Conditions: VSS=AVSS0=VREFL/VREFL0=0V

| Item                                                                         | Sign      | Rated value     | Unit |

|------------------------------------------------------------------------------|-----------|-----------------|------|

| Power supply voltage                                                         | VCC       | -0.3~+4.6       | V    |

| VBATT Power Voltage                                                          | VBATT     | -0.3~+4.6       | V    |

| Input Voltage (Except for ports that correspond to the 5V tolerant (Note 1)) | Vin       | -0.3~VCC+0.3    | V    |

| Input Voltage (Ports that correspond<br>to the 5V tolerant (Note 1))         | Vin       | -0.3~+5.8       | V    |

| Reference Power Voltage                                                      | VREFH     | -0.3~VCC+0.3    | V    |

| Analog Power Voltage                                                         | AVCC      | -0.3~+4.6       | V    |

| Analog Input Voltage                                                         | XLAD,YUAD | -0.3~VCC+0.3V   | V    |

| Operation temperature                                                        | Topr      | -40~+85         | °C   |

| Storage temperature                                                          | Tstg      | $-55 \sim +125$ | °C   |

[Precautions] When the LSI is used in excess of its absolute maximum rating, it may be permanently damaged.

(Note 1) The RXD and MISO pins correspond to the 5V tolerant.

### 4-2 Recommended Operating Conditions

| Table 4-2 Recommen | ded Operating Conditions |

|--------------------|--------------------------|

|--------------------|--------------------------|

| Item                    | Sign   | Rated value    | Unit |

|-------------------------|--------|----------------|------|

| Power supply voltage    | VCC    | $2.7 \sim 3.6$ | V    |

| VBATT Power Voltage     | VBATT  | $2.7 \sim 3.6$ | V    |

| Reference Power Voltage | VREFH0 | 2.7~AVCC0      | V    |

| Reference Power Voltage | VREFH  | $2.7 \sim 3.6$ | V    |

| Analog Power Voltage    | AVCC0  | $2.7 \sim 3.6$ | V    |

#### 4-3 DC Characteristics

Table 4-3 DC Characteristics (1)

Conditions: VCC=AVCC0=VREFH=VBATT=2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

|                                             | Item                         | Sign                       | min               | typ | max              | Unit |

|---------------------------------------------|------------------------------|----------------------------|-------------------|-----|------------------|------|

| Schmidt Trigger                             | Ports corresponding to       | $V_{\rm IH}$               | VCC×0.8           | _   | 5.8              | V    |

| Input Voltage                               | 5V Tolerant                  | $V_{\rm IL}$               | -0.3              | _   | $VCC \times 0.2$ | V    |

|                                             |                              | $\Delta  V_{\rm T}$        | $VCC \times 0.06$ | —   | _                | V    |

|                                             | Ports except for ports       | $V_{\rm IH}$               | VCC×0.8           | _   | VCC+0.3          | V    |

|                                             | corresponding to $5V$        | $V_{IL}$                   | -0.3              | _   | $VCC \times 0.2$ | V    |

|                                             | Tolerant<br>Other Input Pins | $\DeltaV_{T}$              | VCC×0.06          | _   | _                | V    |

| Input High Level                            | MD pin, EMLE                 |                            | $VCC \times 0.9$  | —   | VCC+0.3          | V    |

| Voltage<br>(Normal Input or                 | EXTAL,MISO,EDREQ             | <b>T</b> 7                 | VCC×0.8           | —   | VCC+0.3          | V    |

| Input/Output                                | XCIN                         | $V_{IH}$                   | —                 | —   | VCC+0.3          | V    |

| Pins)                                       | D0~D15                       |                            | $VCC \times 0.7$  | —   | VCC+0.3          | V    |

| Input Low Level                             | MD pin, EMLE                 |                            | -0.3              | —   | $VCC \times 0.1$ | V    |

| Voltage (Normal<br>Input or<br>Input/Output | EXTAL,MISO,EDREQ             | 17                         | -0.3              | —   | $VCC \times 0.2$ | V    |

|                                             | XCIN                         | $\mathrm{V}_{\mathrm{IL}}$ | -0.3              | _   | -                | V    |

| Pins)                                       | D0~D15                       |                            | -0.3              | _   | VCC×0.3          | V    |

Table 4-4 DC Characteristics (2)

Conditions: VCC=AVCC0=VREFH=VBATT =2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

|                   | Item |       |          |     | min     | typ | max | Unit |

|-------------------|------|-------|----------|-----|---------|-----|-----|------|

| Output<br>Voltage | High | Level | IOH=-1mA | Vон | VCC-0.5 | _   | _   | V    |

| Output<br>Voltage | Low  | Level | IoL=1mA  | Vol | _       | _   | 0.5 | V    |

#### Table 4-5 Allowable Output Current

Conditions: VCC=AVCC0=VREFH=VBATT =2.7 - 3.6V, VREFH0=2.7V - AVCC0, VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

| Item                                  | Drive           | Sign | min | typ | max  | Unit |

|---------------------------------------|-----------------|------|-----|-----|------|------|

| Output Low Level Allowable<br>Current | Normal<br>Drive | Iol  | —   |     | 2.0  | mA   |

| (Average Current Value per<br>Pin)    | High Drive      | Iol  | _   |     | 3.8  | mA   |

| Output Low Level Allowable<br>Current | Normal<br>Drive | Iol  | _   | ĺ   | 4.0  | mA   |

| (Maximum Current Value per Pin)       | High Drive      | Iol  | —   |     | 7.6  | mA   |

| Output Low Level Allowable<br>Current | Normal<br>Drive | Іон  | —   | _   | -2.0 | mA   |

| (Average Current Value per<br>Pin)    | High Drive      | Іон  | —   |     | -3.8 | mA   |

| Output Low Level Allowable<br>Current | Normal<br>Drive | Іон  | _   |     | -4.0 | mA   |

| (Maximum Current Value<br>per Pin)    | High Drive      | Іон  | _   |     | -7.6 | mA   |

#### 4-4 Consumption Current

Table 4-6 Consumption Current

Conditions: VCC=AVCC0=VREFH=VBATT =2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

| Item                    | Sign                | min | typ | max  | Unit    |

|-------------------------|---------------------|-----|-----|------|---------|

| Normal operation        | Lun                 |     | 50  | 100  | mA      |

| Low power consumption   | $I_{CC}$            |     | 22  | 200  | $\mu A$ |

| Analog Dowon Curront    | IAVCC0              |     | 2.3 | 3.2  | mA      |

| Analog Power Current    | IVREFH              |     | 1.0 | 1.65 | mA      |

| Reference Power Current | I <sub>VREFH0</sub> |     | 0.6 | 0.7  | mA      |

#### 4-5 AC Characteristics

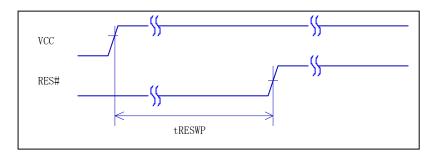

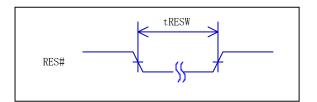

#### 4-5-1 Reset Timing

Table 4-7 Reset Timing

Conditions: VCC=AVCC0=VREFH=VBATT=2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

|       | Ite   | em                          | Sign          | min | typ | max | Unit | Note     |

|-------|-------|-----------------------------|---------------|-----|-----|-----|------|----------|

| RES#  | Pulse | When the power is turned on | ${ m treswp}$ | 2   | —   | _   | ms   | Fig. 4-1 |

| Width |       | Except for the above        | $t_{RESW}$    | 200 | —   | _   | μs   | Fig. 4-2 |

Fig. 4-1 Reset Input Timing when the power is turned on

Fig. 4-2 Reset Input Timing

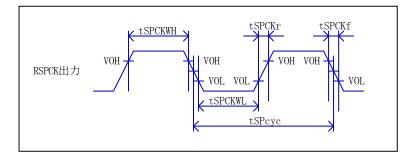

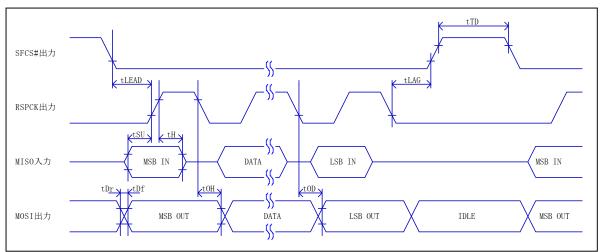

### 4-5-2 SPI Timing

#### Table 4-8 SPI Timing

### Conditions: VCC=AVCC0=VREFH=VBATT=2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

| Item                          |                        | Sign                          | min   | typ   | max      | Unit     | Condition |

|-------------------------------|------------------------|-------------------------------|-------|-------|----------|----------|-----------|

| DODOK Clash Crah              |                        | 4                             | _     | 12    | —        | MHz      | Fig. 4-3  |

| RSPCK Clock Cy                | ycie                   | $\mathrm{t}_{\mathrm{SPcyc}}$ |       | 83.33 |          | ns       | C=30pF    |

| RSPCK Clock                   |                        | tspckwh                       | 33.67 |       |          | ns       |           |

| High Level Puls               | e Width                | USPUKWI                       | 00.01 |       |          | 115      |           |

| RSPCK Clock                   |                        | tspckwl                       | 33.67 | _     | _        | ns       |           |

| Low Level Pulse               | Width                  | USPUKWL                       | 00.01 |       |          | 115      |           |

| RSPCK Clock                   |                        | tspckr,                       | _     | _     | 5        | ns       |           |

| Rise/Fall Time                |                        | ${ m t}_{ m SPCKf}$           |       |       | 0        | 115      |           |

| Data Input                    | $VCC \ge 3.0V$         | tar                           | 15    | _     |          | Fig. 4-4 | 🗵 4-4     |

| Set-up Time                   | VCC<3.0V               | $t_{SU}$                      | 20    | —     | —        | C=30pF   | C=30pF    |

| Data Input Hold               | Data Input Hold Time   |                               | 0     |       |          | ns       |           |

| SFCS# Set-up T                | SFCS# Set-up Time      |                               | 1     |       | _        | us       |           |

| SFCS# Hold Tim                | ne                     | $t_{ m LAG}$                  | 1     | _     |          | us       |           |

| Data Output Del               | Data Output Delay Time |                               |       |       | 18       | ns       |           |

| Data Output Hold Time         |                        | ton                           | 0     |       |          | ns       |           |

| Continuous Transmission Delay |                        | $t_{ m TD}$                   | 200   | _     | _        | ns       |           |

|                               | Time                   |                               | 200   |       |          | 110      |           |

| MOSI                          |                        | tdr, tdf                      | —     | —     | <b>5</b> | ns       |           |

| Rise/Fall Time                |                        |                               |       |       |          |          |           |

Fig. 4-3 SPI Clock Timing

Fig. 4-4 SPI Timing (SPI Mode: Mode 0)

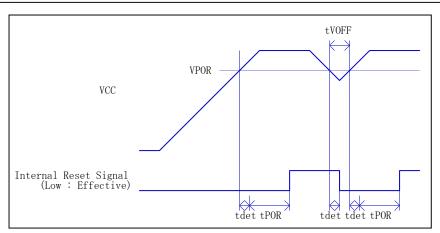

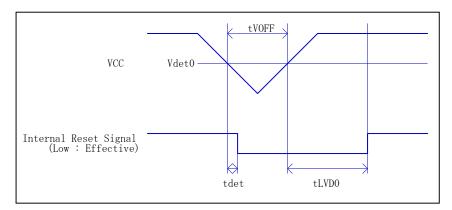

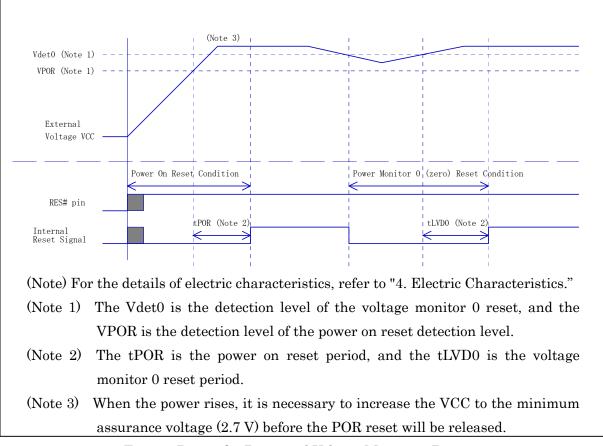

#### 4-6 Power On Reset Circuit, Voltage Detection Circuit Characteristics

Table 4-9 Power On Reset Circuit, Voltage Detection Circuit Characteristics Conditions: VCC=AVCC0=VREFH=VBATT=2.7 - 3.6V, VREFH0=2.7V - AVCC0, VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

|                       | Item                                | Sign               | min | typ  | max | Unit    | Condition             |

|-----------------------|-------------------------------------|--------------------|-----|------|-----|---------|-----------------------|

| Voltage<br>Detection  | Power On Reset<br>(POR)             | VPOR               | 2.5 | 2.6  | 2.7 | V       | Fig. 4-5              |

| Level                 | Voltage Detection<br>Circuit (LVD0) | V <sub>det</sub> 0 | 2.7 | 2.80 | 2.9 | V       | Fig. 4-6              |

| Internal<br>Reset     | Power On Reset<br>Time              | tpor               |     | 4.6  |     | ms      | Fig. 4-5              |

| Time                  | LVD0 Reset Time                     | $t_{LVD0}$         |     | 4.6  |     | ms      | Fig. 4-6              |

| Minimum VCC Drop Time |                                     | $t_{VOFF}$         | 200 | _    | _   | μs      | Fig. 4-5,<br>Fig. 4-6 |

| Response Delay Time   |                                     | $t_{\rm det}$      |     | _    | 200 | $\mu s$ | Fig. 4-5,<br>Fig. 4-6 |

Fig. 4-5 Power On Reset Timing

Fig. 4-6 Voltage Detection Circuit Timing (Vdet0)

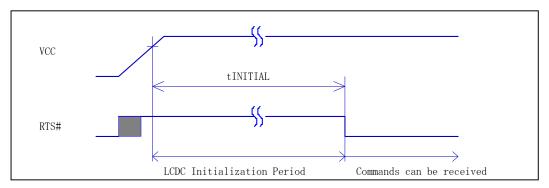

### 4-7 Start-up Time of LCD Controller

Table 4-10 LCD Controller Start-up Time

Conditions: VCC=AVCC0=VREFH=VBATT=2.7 - 3.6V, VREFH0=2.7V - AVCC0,

VSS=AVSS0= VREFL/VREFL0=0V, Ta=Topr

| Item                            | Sign                            | min | typ | max | Unit | Note     |

|---------------------------------|---------------------------------|-----|-----|-----|------|----------|

| Start-up Time of LCD Controller | $\mathbf{t}_{\mathrm{INITIAL}}$ | 450 |     | 660 | ms   | Fig. 4-7 |

$(\mbox{Note})~\mbox{When the microSD}$  card is not used, Start-up time is minimum value.

When the microSD card is used, Start-up time is miximum value.

Fig. 4-7 LCD Controller Start-up Time

### 5. Clock

### 5-1 Overview

The LCD controller includes a clock oscillation circuit.

The input/output pins of the clock oscillation circuit are shown in Table 5-1.

|          |              | 1                                                       |

|----------|--------------|---------------------------------------------------------|

| Pin Name | Input/Output | Function                                                |

| XTAL     | Output       | These are the crystal oscillator pins of the main clock |

| EXTAL    | Input        | oscillation circuit.                                    |

| XCIN     | Input        | These are the crystal oscillator pins of the sub clock  |

| XCOUT    | Output       | oscillation circuit. The LCD controller is not used.    |

Table 5-1 Input/Output Pins of Clock Oscillation Circuit

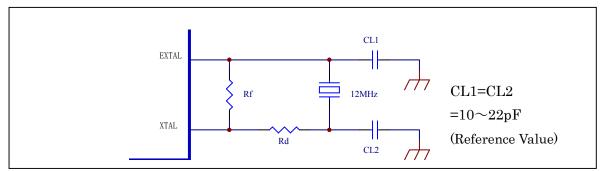

#### 5-2Main Clock Oscillator

Connect the crystal oscillator with an oscillation frequency of 12MHz to the main clock oscillator.

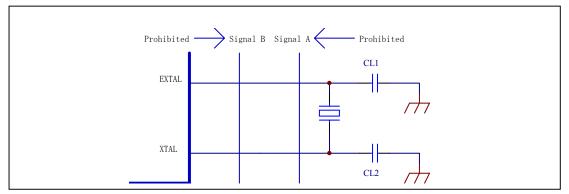

The example of connection when connecting the crystal oscillator is shown in Fig. 5 - 1.

Insert a damping resistance (Rd) if necessary. The resistance value varies with an oscillator and an oscillation drive capability. Thus, set a value that is recommended by the oscillator manufacturer. In addition, when additional external feedback resistance (Rf) is required by the oscillation manufacturer, insert the resistance Rf between the EXTAL and the XTAL.

Fig. 5-1 Example of Connection for Crystal Oscillator

| Table 5-2 Damping Resistance Rd (Reference Value) |    |  |  |  |

|---------------------------------------------------|----|--|--|--|

| Frequency of Crystal Oscillator [MHz]             | 12 |  |  |  |

| Rd $[\Omega]$                                     | 0  |  |  |  |

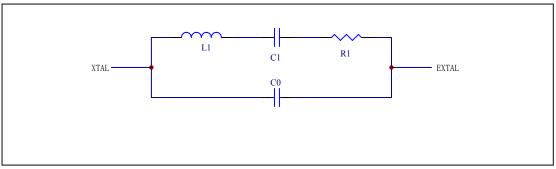

The equivalent circuit of the crystal oscillator is shown in Fig. 5-2. Use a crystal oscillator with the characteristics as those shown in Table 5-3.

However, the characteristics are just a reference value. Even if the characteristics are not satisfied, there is no problem when the connection circuit including the substrate is matched.

Fig. 5-2 Equivalent Circuit for Crystal Oscillator

| Frequency [MHz] | 12 |

|-----------------|----|

| R1max [Ω]       | 60 |

| C0max[pF]       | 7  |

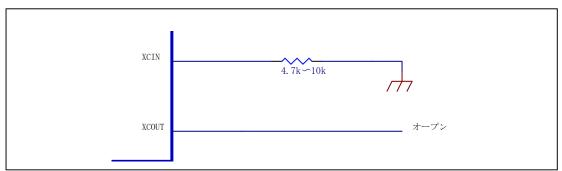

### 5-3 Sub Clock Oscillator

The LCD controller has not used a sub clock oscillator.

Connect (pull down) the XCIN pin by means of a resistance  $(4.7k\Omega \sim 10k\Omega)$  to the VSS (GND), as shown in Fig. 5-3. Open the XCOUT pin.

Fig. 5-3 Pin Treatment of Sub Clock Oscillator

### 5-4 Precautions for Use

### 5-4-1 Precautions for Crystal Oscillator

Characteristics for the oscillator have a close relationship with the board that is designed by a user. Then, the user shall sufficiently evaluate them and then use the

oscillator by reference to the example of connection that is described in this chapter. The circuit constants of the oscillator vary with the stray capacitance in the packaging circuit. Thus, the user should check with the oscillator manufacturer to determine the matching conditions. Make sure that the voltage that is applied to the oscillator pins does not exceed the maximum rating.

#### 5-4-2 Precautions for Board Design

Arrange the oscillator and the capacitor at the nearest locations of the oscillator pins. Do not arrange signal lines close to the oscillator circuit, as shown in Fig. 5-4. The electromagnetic induction that is generated by the close arrangement above may interfere with the normal oscillation.

Fig. 5-4 Precautions for Board Design of Oscillation Circuit

#### 5-4-3 Oscillation Stability Time

Set the oscillator stability time of the crystal oscillator at 20 msec or less. (the oscillation stability time between the application of a voltage to the crystal oscillator and the stabilization of amplitude).

#### 5-5 Reference Circuit

For the oscillator circuits and constants of the crystal oscillator that are evaluated with our board, refer to "23. Reference Circuit Diagram."

The manufacturer and type of the crystal oscillators that are used in our boards are described in Table 5-4.

| Manufacturer      | Туре                       |

|-------------------|----------------------------|

| Nihon Dempa Kogyo | NX3225GA-12.000M-STD-CRG-2 |

### 6. Reset

#### 6-1 Overview

There are Resets by RES# Pin, Power On Reset, and Voltage Monitor 0 (zero) Reset. The names and causes of Resets are shown in Table 6-1.

| Name of Reset                  | Cause                                           |  |  |  |  |

|--------------------------------|-------------------------------------------------|--|--|--|--|

| RES# Pin Reset                 | The input voltage of RES# pin is Low.           |  |  |  |  |

| Power On Reset                 | VCC increases (Monitor voltage: VPOR) (Note 1)  |  |  |  |  |

| Voltage Monitor 0 (zero) Reset | VCC decreases (Monitor voltage: Vdet0) (Note 1) |  |  |  |  |

(Note 1) For the Monitor voltages (VPOR, Vdet0), refer to "4. Electric characteristics."

The input/output pins for the reset are shown in Table 6-2

| Table 6-2 Input/Output Pins for Reset |              |           |  |

|---------------------------------------|--------------|-----------|--|

| Pin Name                              | Input/Output | Function  |  |

| RES#                                  | Input        | Reset Pin |  |

#### 6-2 RES# Pin Reset

This is Reset by the RES# Pin.

When the RES# pin is Low, the LCD controller ceases the operation and enters the reset condition.

For the reset timing, refer to "4. Electric Characteristics."

#### 6-3 Power On Reset and Voltage Monitor 0 (zero) Reset

The power on reset is an internal reset by the power on reset circuit.

When turning the power on under the condition that the RES# pin is set to High, the power on reset is activated. When the power voltage VCC exceeds the monitor voltage VPOR, the internal reset is released after the power on reset time. Then, the LCD controller begins its operation.

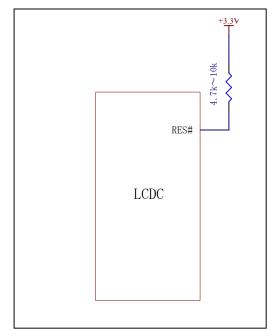

When performing the power on reset, pull up the RES# pins with a resistance of  $4.7k\Omega - 10k\Omega$ , as shown in Fig. 6-1.

The voltage monitor 0 (zero) reset is an internal reset by the power monitor circuit. When the VCC is Vdet0 or lower, the LCD controller enters the reset condition. When the VCC exceeds the Vdet0, the reset of the LCD controller is released after the LVD0 reset time (tLVD0.)

An example of operation of the power on reset and the voltage monitor 0 reset is

shown in Fig. 6-2.

Fig. 6-1 Circuit when the Power On Reset is performed

Fig. 6-2 Power On Reset and Voltage Monitor 0 Reset

### 6-4 Reference Circuit

Refer to "23 Reference Circuit Diagrams" that describes the reset reference circuits by the power on reset.

## 7. Serial Communication Interface (SCI)

### 7-1 Overview

The LCD controller includes one channel of asynchronous serial communication interface (hereinafter called SCI).

The input/output pins for the SCI are shown in Table 7-1.

|          | r · · · r    |                                     |  |  |

|----------|--------------|-------------------------------------|--|--|

| Pin Name | Input/Output | Function                            |  |  |

| RXD      | Input        | SCI Receive Data Input Pin          |  |  |

| TXD      | Output       | SCI Transmission Data Output Pin    |  |  |

| RTS#     | Output       | SCI Transmission Request Output Pin |  |  |

| BAUDSEL1 | Input        | SCI Baud Rate Selection Pins        |  |  |

| BAUDSEL0 | Input        |                                     |  |  |

Table 7-1 SCI Input/Output Pins

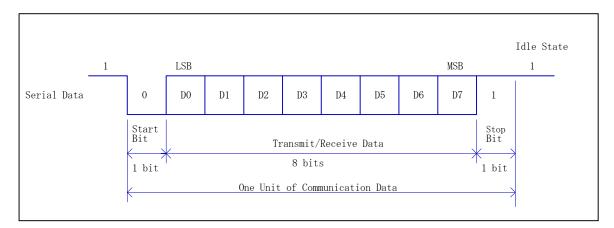

#### 7-2 Communication spetifications

#### 7-2-1 Communication specifications

The SCI communication specifications are shown in Fig. 7-2.

| Item             | Specifications                                           |

|------------------|----------------------------------------------------------|

| Baud Rate        | Selectable from among 9600, 19200, 38400, and 115200 bps |

| Data Length      | 8 bits                                                   |

| Stop Bit         | 1 bit                                                    |

| Parity           | Not provided                                             |

| Hardware Control | RTS Control                                              |

The data format of the asynchronous serial communication is shown in Fig. 7-1.

Fig. 7-1 Data Format of Asynchronous Serial Communication

#### 7-2-2 Baud Rate Selection

The Baud Rates can be selected from among 9600, 19200, 38400, and 115200bps by connecting the BAUDSEL1 and BAUDSEL0 pins to the DIP switches.

The relationship between the BAUDSEL1 and BAUDSEL0 pins and the Baud Rates is shown in table 7-3.

| BAUDSEL1 Pin | BAUDSEL0 Pin | Baud Rate [bps] |

|--------------|--------------|-----------------|

| LOW          | LOW          | 9600            |

| LOW          | HIGH         | 19200           |

| HIGH         | LOW          | 38400           |

| HIGH         | HIGH         | 115200          |

Table 7-3 Relationship between BAUDSEL1 and BAUDSEL0 pins and Baud Rates

The BAUDSEL1 and BAUDSEL0 pins are pulled up in the LCD controller. When setting the above pins to HIGH, these pins may be open.

These pin conditions are checked only when the power is turned on. Thus, when the baud rate is changed, the power should be restarted or reset again.

#### 7-3 Receive Buffer and RTS# Control

The LCD controller includes receive buffers of 512 bytes. The receive buffers are ring buffers.

When the receive data that is stored in the receive buffer is not been processed, or if the pointer has passed through the buffer, the unprocessed data may have been overwritten.

To prevent the above, the LCD controller includes the RTS# output pin.

The relationship between the output condition of the RTS# output pin and the receive feasibility is shown in Table 7-4.

| Table 7.4 Output Condition of R15# Output 1 in and Receive Feasibility |                     |  |

|------------------------------------------------------------------------|---------------------|--|

| Output Condition of RTS# Output Pin                                    | Receive Feasibility |  |

| HIGH                                                                   | Reception unable    |  |

| LOW                                                                    | Reception enable    |  |

Table 7-4 Output Condition of RTS# Output Pin and Receive Feasibility

When commands are received continually during the drawing process, if the pointer has passed through the buffer, the received, but unprocessed data may have been overwritten. Thus, connect the RTS# pin of the LCD controller to the CTS# pin of the user's microcomputer, and then use the Controller.

#### 7-4 Precautions for Use

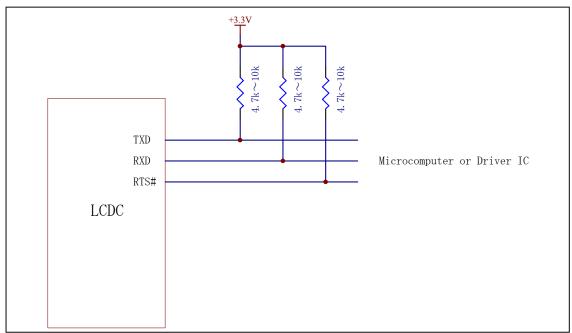

The pins related to the SCI are the input ports during the reset process. During the reset process, signals are unstable. Thus, pull up signals with a resistance ( $4.7k\Omega - 10k\Omega$ ), as shown in Fig. 7-2.

Fig. 7-2 Pull-up Processing of SCI Signals

#### 7-5 Reference Circuit

Refer to "23. Reference Circuit Diagrams" that describes the reference circuits when the driver IC is not used.

### 8. Frame Buffer Memory

#### 8-1 Overview

The LCD controller includes an external bus controller, which allows one to connect a frame buffer memory (SRAM) on a maximum capacity of 256K words, 16 bits. The input/output pins for the external bus are shown in Table 8-1.

| Pin Name | Input/Output | Function                                    |  |

|----------|--------------|---------------------------------------------|--|

| A18~A1   | Output       | Address Output Pins                         |  |

| D15~D0   | Input/Output | Data Input/Output Pins                      |  |

|          |              | LCD RGB Signals                             |  |

| CS#      | Output       | Chip Select Output Pin                      |  |

| RD#      | Output       | Read Output Pin                             |  |

| WR#      | Output       | Write Output Pin                            |  |

| EDREQ    | Input        | LCD Display Data Transfer Request Input Pin |  |

| HDEN     | Output       | LCD Display Period Output Pin               |  |

Table 8-1 Input/Output Pins for External Bus

#### 8-2 Frame Buffer Memory Access

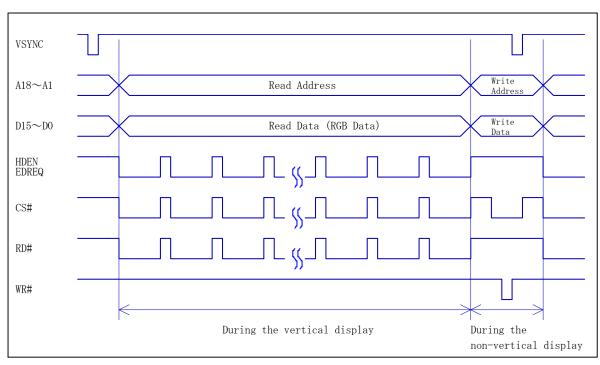

The access to the frame buffer memory is shown in Fig. 8-1.

During the veridical display, the read access is started by the LCD display period output signal (output from the HDEN pin) and the data is read from the frame buffer memory. The data that is output on the data bus is the RGB signals of the LCD. During the vertical display, the drawing data cannot be written in the frame buffer memory. The drawing data is written in the frame buffer memory with commands for drawing during the non-vertical display. If the drawing data cannot be written during the non-vertical display due to image size, the remaining data will be written during the non-vertical display of the next frame.

Fig. 8-1 Access of Frame Buffer Memory

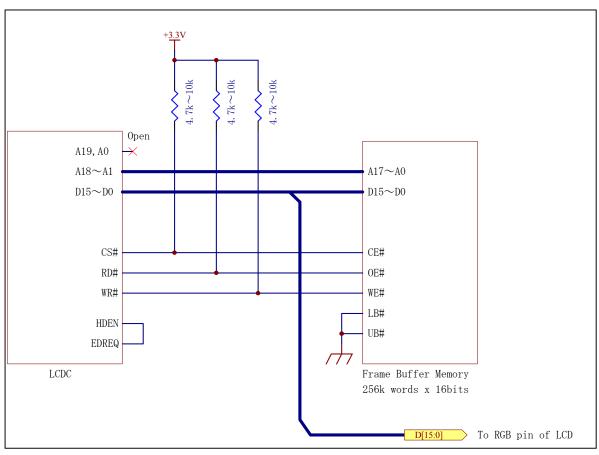

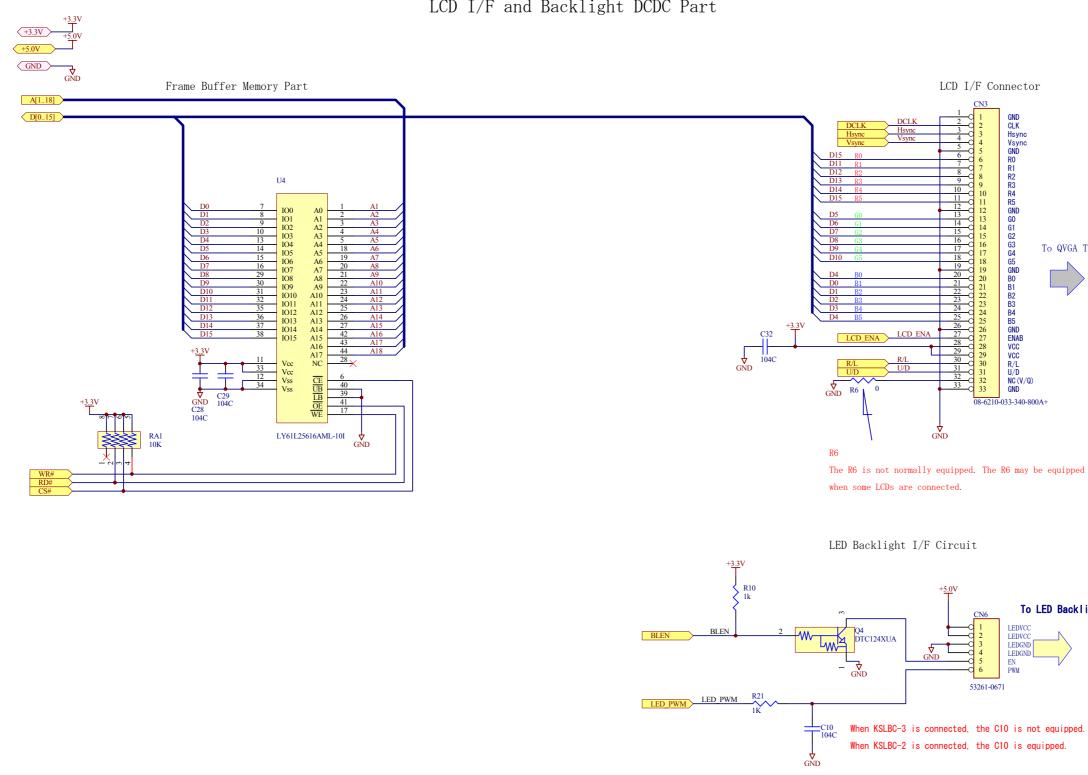

#### 8-3 Connection

The connection diagram between the LCD controller and the frame buffer memory is shown in Fig. 8-2.

Connect the address signal of the LCD to the address pins of the buffer memory, in order from A1, because of the data bus width has 16 bits. The LCD controller includes the pins of A19 and A0. Open these pins.

Connect the data bus to the D15 - D0 pins and the RGB pins of the LCD. For the connection to the LCD, refer to "9 LCD Interface."

For the CS#, RD#, and WR# signals, connect the CE#, OE#, and WE# of the frame buffer memory. These pins are input ports during the reset process. During the reset process, signals are unstable and thus, malfunctions such as writing and/or outputting of unnecessary data may occur. Pull up the signals with resistance ( $4.7k\Omega$ -  $10k\Omega$ ), as shown in Fig. 8-2.

Connect the HDEN pin and the EDREQ pin. Make sure that, if these pins are not connected, the RGB signals will not be outputted to the LCD during the vertical display.

Fig. 8-2 Connection Diagram of Frame Buffer Memory

#### 8-4 Memory Map

The memory map of the buffer memory is shown in Fig. 8-3.

The LCD controller is configured with three pages. One page of them is allocated to QVGA display area.

The pages can be selected as a display or a write page by commands.

For more detail of the commands, refer to "Command-driven LCD Controller IC Command Manual."

Fig. 8-3 Memory Map of Frame Buffer Memory

#### 8-5 Precautions for Use

#### 8-5-1 Selection of Frame Buffer Memory

Use the buffer memory of a high speed SRAM (a speed of 10 nsec.). The manufacturer and type of the high speed SRAM we recommend are shown in Table 8-2.

|              | 51 8                 | - P               |

|--------------|----------------------|-------------------|

| Manufacturer | Туре                 | Specifications    |

| Lyontek      | LY61L25616AML-10I    | 256k×16 bit, 10ns |

| ISSI         | IS61WV25616BLL-10TLI | 256k×16 bit, 10ns |

Table 8-2 Manufacturer and Type of High Speed SRAM

When using a high speed SRAM that is not listed in Table 8-2, select a high speed SRAM that has equivalent specifications to the SRAM in Table 8-2.

#### 8-5-2 Precautions for Board Design

Arrange the signal lines between the LCD controller and the frame buffer memory with a minimum length.

### 8-6 Reference Circuit

Refer to "23. Reference Circuit Diagrams" that describes the reference circuits when LY61L25616AML-10I (Lyontek) is connected.

### 9. LCD Interface

#### 9-1 Overview

The LCD controller allows one to output the LCD synchronization signal and control signals for the LCD.

The output pins for the LCD interface are shown in Table 9-1.

| Pin Name    | Input/Output | Function                                     |  |

|-------------|--------------|----------------------------------------------|--|

| DCLK        | Output       | Dot Clock Output Pin                         |  |

| HSYNC       | Output       | Horizontal Synchronization Signal Output Pin |  |

| VSYNC       | Output       | Vertical Synchronization Signal Output Pin   |  |

| ENAB        | Output       | Data Enabling Output Pin                     |  |

| R/L         | Output       | Horizontal Inverse Signal Output             |  |

| U/D         | Output       | Vertical Inverse Signal Output               |  |

| DCLK_INVERT | Input        | DCLK Inverse Input                           |  |

Table 9-1 Output Pins for LCD Interface

#### 9-2 Connection

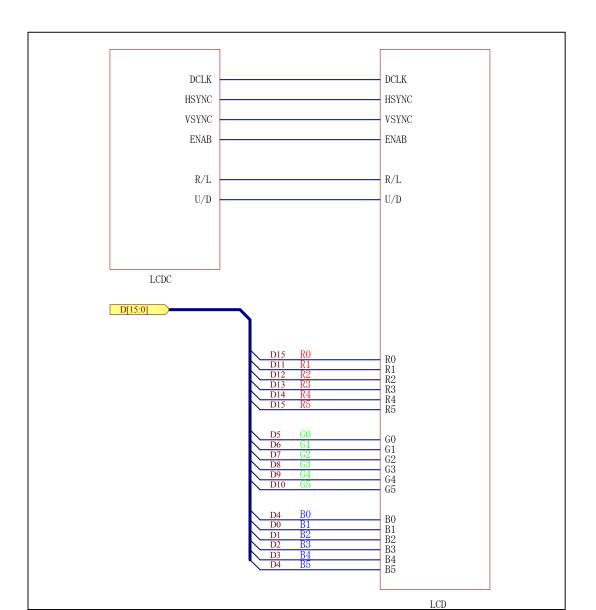

The connection diagram between the LCD controller and the LCD is shown in Fig. 9-1.

There are LCDs without the ENAB signal and LCDs with only an ENAB signal that is a synchronization signal. Connect between the LCDC and the LCD with a connection method suited to the LCD that is used.

The LCD controller does not include the RGB output Pins. As explained in "8. Frame Buffer Memory", the RGB data is outputted to the data busses of D15 - D0 during the vertical display. Connect the data busses of D15 - D0 to the RGB signals of the LCD, as shown in Fig. 9-1.

The LCD controller includes the R/L terminals (a horizontally inverted signal output) and the U/D terminals (a vertically inverted signal output). The indication direction in the LCD can be changed by connecting the R/L and U/D terminals on the LCD side. The output logical values of the R/L and U/D terminals can be set by commands. For more detail of the commands, refer to "Command-driven LCD Controller IC Command Manual." The state of these terminals' initial output logic values are shown in Table 9-2.

| Table 9-2 Initial Output Logic Values of R/L and U/D Terminals |                            |  |

|----------------------------------------------------------------|----------------------------|--|

| Terminal Name                                                  | Initial Output Logic Value |  |

| R/L terminals                                                  | LOW Output                 |  |

| U/D Terminals                                                  | HIGH Output                |  |

| 0/D Terminais                                                  |                            |  |

Fig. 9-1 Connection of LCD

#### 9-3 Object LCD

LCDs whose operations have been checked by this LCD controller are described on our web site. Refer to the site.

$$-35-$$

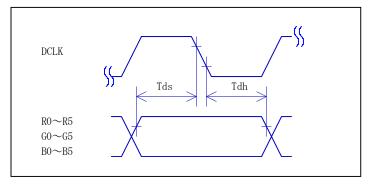

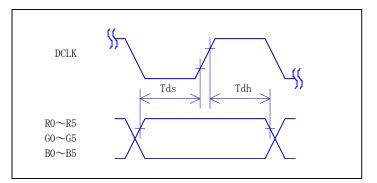

#### 9-4 DCLK Polarity Reversing Function

The LCD controller includes a function that reverses the polarity of the DCLK output signal. The polarity is reversed by the DVLK\_INVERT input terminals. The relationship of the input logic values of the DCLK\_INVERT input terminals to the polarities of the DCLK\_INVERT output signals is shown in Table 9-3.

| Table 9-3 Relationship of Input Logic |                         |          |  |

|---------------------------------------|-------------------------|----------|--|

| DCLK_INVERT                           | Polarity of DCLK_INVERT | Remarks  |  |

| Input Terminal                        | Output Signal           |          |  |

| HIGH or Open                          | Falling                 | Fig. 9-2 |  |

| LOW Rising                            |                         | Fig. 9-3 |  |

Fig 9-2 Falling Polarity of DCLK Output Signal

Fig. 9-3 Rising Polarity of DCLK Output Signal

#### 9-5 Reference Circuit

Refer to "23. Reference Circuit Diagrams" that describes the reference circuits when the following LCD is connected.

- Kyocera TCG057QVLCS-H50

- Kyocera TCG057QVLCA-G00

- DENSITRON LMTM057QVGNCA-4R

## 10. SPI Interface

### 10-1 Overview

The LCD controller includes one channel of serial peripheral interface (hereinafter called SPI).

The SPI is used for communication between the LCD controller, and the serial flash memory and/or the micro SD card. The LCD controller is a master side.

The input/output pin for SPI is shown in Table 10-1.

| Pin Name | Input/Output | Function                                 |

|----------|--------------|------------------------------------------|

| RSPCK    | Output       | Clock Output Pin                         |

| MOSI     | Output       | Master Data Output Pin                   |

| MISO     | Input        | Master Data Input Pin                    |

| SDCCS#   | Output       | microSD Card Selecting Output Pin        |

| SFCS#    | Output       | Serial Flash Memory Selecting Output Pin |

Table 10-1 SPI Input/Output Pins

### 10-2 Communication Specifications

The SPI communication specifications are shown in Fig. 10-2.

| Item                        | Specifications          |  |

|-----------------------------|-------------------------|--|

| Transfer Rate               | 12Mbps (Note 1)         |  |

| Communication Activity Mode | Full-duplex Synchronous |  |

|                             | Serial Communication    |  |

| SPI Mode                    | Mode 0                  |  |

Table 10-2 SPI Communication Specifications

(Note 1) Only during initialization of the microSD card, the transfer rate is 400 kbps.

### 10-3 Connection

The connection diagram between the LCD controller, and the serial flash memory and/or the micro SD card is shown in Fig. 10-1. Pull down the RSPCK with a register of  $100k\Omega$ . Pull up with a resister of  $47k\Omega$  for signals except for the RSPCK.

When the LCD controller is not connected to the serial flash memory and the microSD card, treat each Pin, as shown in Table 10-3.

Fig. 10-1 SPI Connection

| Pin Name | Input/Output | Pin Treatment                         |

|----------|--------------|---------------------------------------|

| RSPCK    | Output       | Pull-up $(4.7k\Omega \sim 10k\Omega)$ |

| MOSI     | Output       | Pull-up $(4.7k\Omega \sim 10k\Omega)$ |

| MISO     | Input        | Pull-up $(4.7k\Omega \sim 10k\Omega)$ |

| SDCCS#   | Output       | Open                                  |

| SFCS#    | Output       | Open                                  |

#### 10-4 Reference Circuit

Refer to "23. Reference Circuit Diagrams" that describes the reference circuits when the LCD controller is not connected to the serial flash memory and the microSD card. For Starter Kit users, refer to the circuit diagrams attached to the Starter Kit that describes the connection circuit for the serial flash memory and the microSD card.

# 11. Serial Flash Memory

### 11-1 Overview

The LCD controller includes a font drawing function and an image data drawing function. When using these functions, it is necessary to connect the serial flash memory to the LCD controller and to write the font data or the image data in the memory.

However, the LCD controller includes the 16-dot font data for the font image function. When drawing the 24-dot font characters, it needs the serial flash memory.

### 11-2 Memory Map

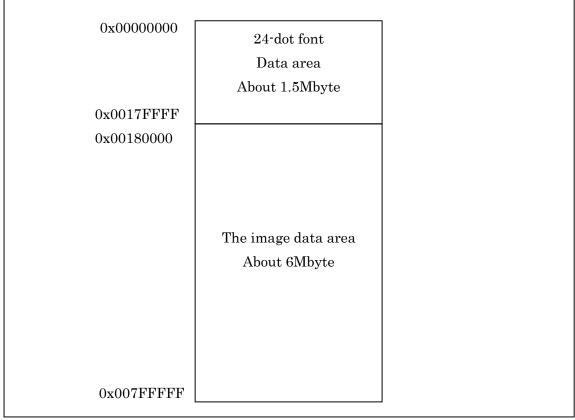

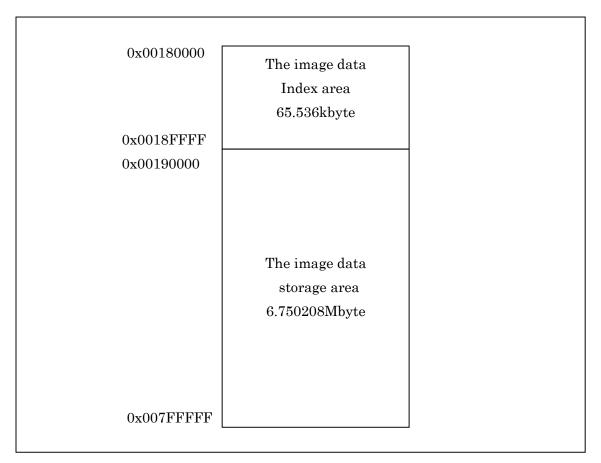

The memory map of the serial flash memory is shown in Fig. 11-1.

Fig. 11-1 Memory Map of Serial Flash Memory

The image data area is divided into the image data index area and the image data storage area, as shown in Fig. 11-2.

Fig. 11-2 Image Data Area

The following information is stored in the image data index area.

①Image data width (2 bytes)

②Image data height (2 bytes)

③Starting address of Image data location (4 bytes)

The image data (color information) is stored in the image data storage area. The size of the image data index area is 65,536 Kbytes. This enables one to write image data on a maximum of 8,192 in the serial flash memory. However, the size of the image data may reduce the number of screens that can be written in the memory. For example, in the case of a QVGA size image,

the data for 1 (one) image is 320 x 240 x 2 bytes=153.6Kbytes.

The number of image data that are written in the image data area is 6.750208Mbytes/153.6 Kbytes=43 screens.

In reverse, in the case of an image size of 20 x 20,

one image data is  $20 \times 20 \times 2 = 800$  bytes.

The number of image data that can be written in the image data area is 6.750208Mbytes/800 Kbytes $\Rightarrow$  8,437 screens.

However, the image data index area can store only information of 8,192 image data size at most. In this case, the maximum number of screens that can be written is 8,192.

The number of images that can be stored in the serial flash memory varies with the size of the image data prepared by a user. Be aware of the number of images.

### 11-3 Precautions for Use

### 11-3-1 Selection of Serial Flash Memory

For the serial flash memory, use the serial flash memory manufactured by the specified manufacturer shown in Table 11-1.

| Manufacturer      | Туре         | Specifications  |

|-------------------|--------------|-----------------|

| Micron Technology | M25P64-VMF6P | Capacity 64Mbit |

Contact us when a serial flash memory that is not listed in Table 11-1 is used. We will check to determine whether the data sheet of a serial flash memory that is sent by a user conforms to our requirements. Select a flash memory of 64 Mbit in capacity.

#### 11-3-2 Timeout of Serial Flash Memory

For the following processes of the serial flash memory, time required to complete the processing varies with manufacturer and memory capacity.

- Writing a status register

- Writing a page

- Sector erasing

- $\cdot$  Chip (bulk) erasing

Timeout is invalid by default in the LCD controller, which waits until the above process is completed.

Enabling timeout by a command allows one to end the processing without waiting for the completion of operations when the process is not completed, although the timeout time that is shown in Table 11-2 has been passed over. For more detail of the commands, refer to "Command-driven LCD Controller IC Command Manual."

| Process Description                 | Timeout Time | Unit |

|-------------------------------------|--------------|------|

| Writing a status register           | 30           | msec |

| Writing a page                      | 10           | msec |

| Sector erasing, Chip (bulk) erasing | 320          | sec  |

Table 11-2 Timeout Time

# 12. Touch Panel

### 12-1 Overview

The LCD controller includes a touch panel controller.

The input/output Pins for the touch panels are shown in Table 12-1.

| Pin Name | Input/Output | Function                                                  |

|----------|--------------|-----------------------------------------------------------|

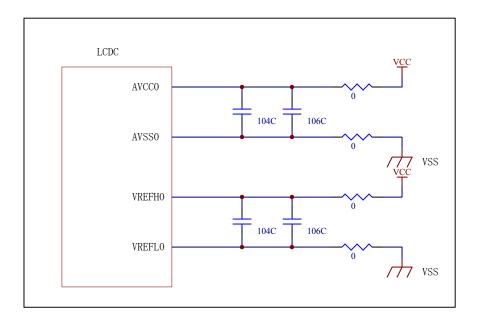

| AVCC0    | Input        | Analog Power Pin of A/D Converter                         |

| AVSS0    | Input        | Analog Ground Pin of A/D Converter                        |

| VREFH0   | Input        | Reference Power Pin of A/D Converter                      |

| VREFL0   | Input        | Reference Power Ground Pin of A/D Converter               |

| XOUT     | Output       | X-axis Voltage Applying Enabling Output Pin               |

| YOUT     | Output       | Y-axis Voltage Applying Enabling Output Pin               |

| XIN      | Output       | X-axis Voltage Applying Signal Output Pin                 |

| YIN      | Output       | Y-axis Voltage Applying Signal Output Pin                 |

| TDRC     | Output       | Touch Panel Detection Resistance Control<br>Output Signal |

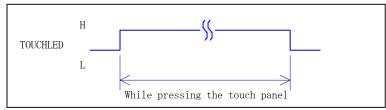

| TOUCHLED | Output       | Touch Panel Pressing Detection Output<br>Signal           |

| XLAD     | Input        | Y-position Detection Voltage Analog Input Pin             |

| YUAD     | Input        | X-position Detection Voltage Analog Input Pin             |

| XD       | Input        | X-direction AD Value Inverted Input Pin                   |

| YD       | Input        | Y-direction AD Value Inverted Input Pin                   |

Table 12-1 Input/Output Pins related Touch Panel

### 12-2 Specifications

The specifications of the touch panel controller are shown in Fig. 12-2.

| Item                        | Specifications                       |

|-----------------------------|--------------------------------------|

| Corresponding Touch Panel   | Four-wire Resistive Type             |

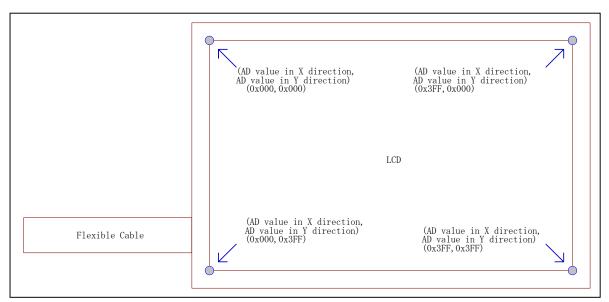

| Touch Panel Data Resolution | 10 bits                              |

| Others                      | X-direction AD Value, Y-direction AD |

|                             | Value Inverted                       |

Table 12-2 Specifications of Touch Panel Controller

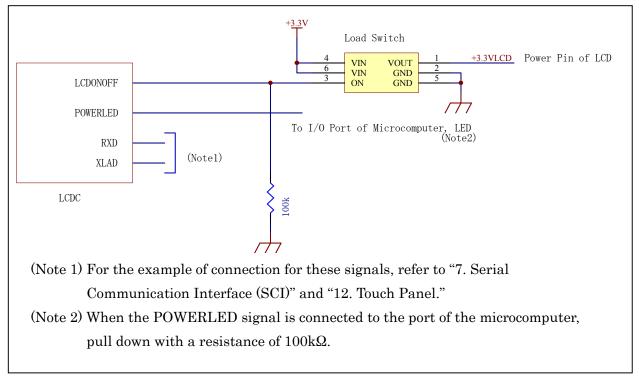

### 12-3 Connection

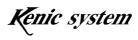

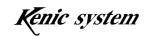

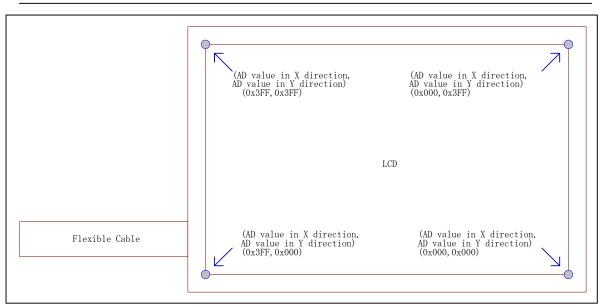

An example of the touch panel connection is shown in Fig. 12-1.

The XD and the YD pins are pulled up in the LCD controller. Thus, the external pull-up resistances are not needed.

When the touch panel is not used, each pin is treated, as shown in Table 12-3.

Fig. 12-1 Touch Panel Connection Example

| Table 12-3 Pin | Treatment when | the touch pane | l is not used |

|----------------|----------------|----------------|---------------|

|----------------|----------------|----------------|---------------|

| Pin Name | I/O    | Pin Treatment                           |

|----------|--------|-----------------------------------------|

| XOUT     | Output | Open                                    |

| YOUT     | Output | Open                                    |

| XIN      | Output | Open                                    |

| YIN      | Output | Open                                    |

| TDRC     | Output | Open                                    |

| TOUCHLED | Output | Open                                    |

| XLAD     | Input  | Pull-down $(4.7k\Omega \sim 10k\Omega)$ |

| YLAD     | Input  | Pull-down $(4.7k\Omega \sim 10k\Omega)$ |

| XD       | Input  | Open (Internal Pull up)                 |

| YD       | Input  | Open (Internal Pull up)                 |

#### 12-4 Touch Panel Data Returning Mode

The LCD controller includes the following touch panel data returning modes.

- ① 1 (one) Data Returning

- ② Automatic continuous returning

- ③ Continuous returning while pressing the touch panel

- ④ Returning only when the touch panel is being pressed

- (5) Returning only when the touch panel is released

- 6 Returning both data when the touch panel is pressed and when it is released

These modes are selected by commands. For more detail of the commands, refer to "Command-driven LCD Controller IC Command Manual."

#### 12-4-1 1 (one) Data Returning

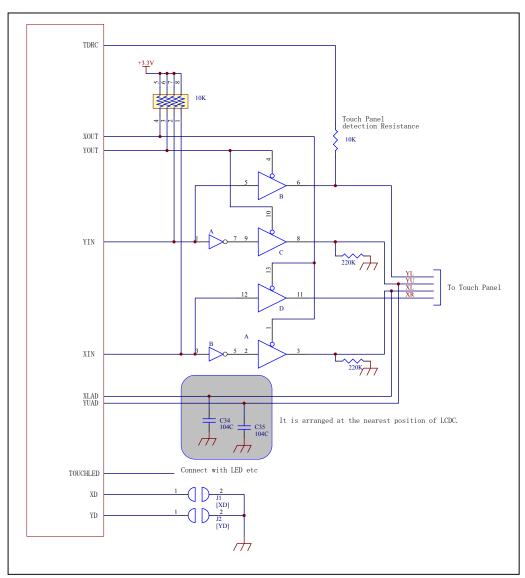

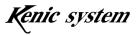

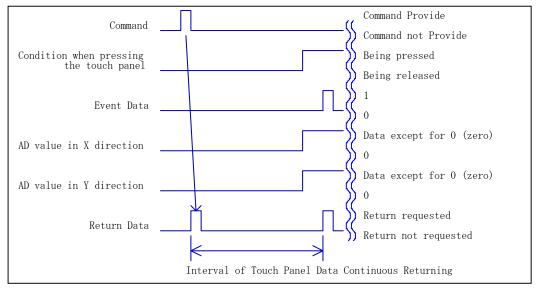

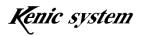

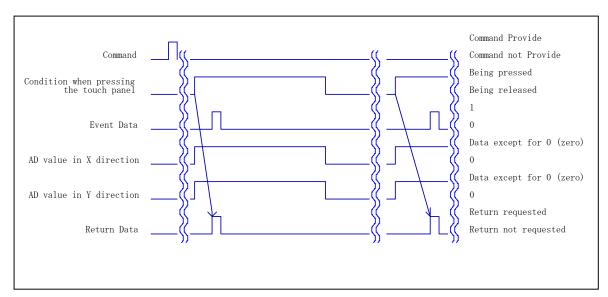

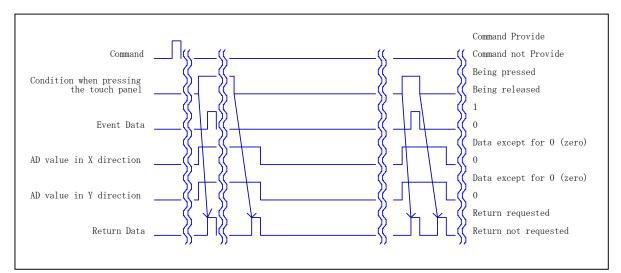

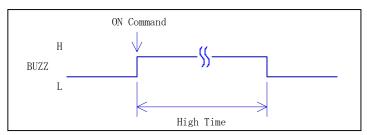

The mode is for returning the touch panel data once, (the event data, the X-direction AD value and the Y-direction AD value) when a command is received. The operation is shown in Fig. 12-2.